# Front end design methodology. Synthesis, timing closure

March 2019

Moscow

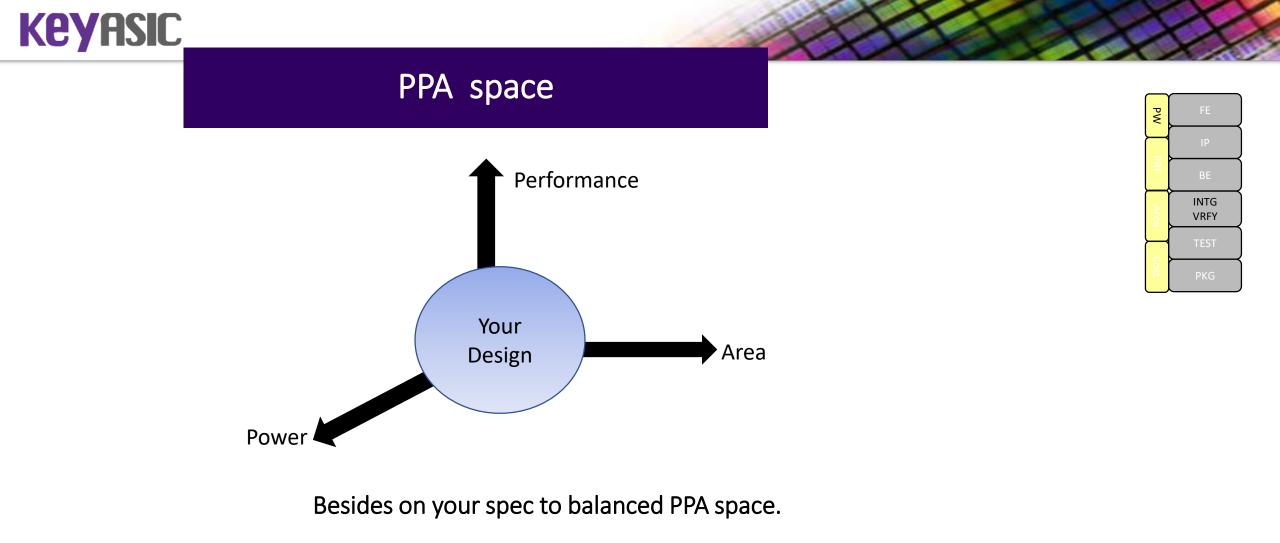

EX: You want design the max Power.

In the FE begin, you need consider in mind for Power

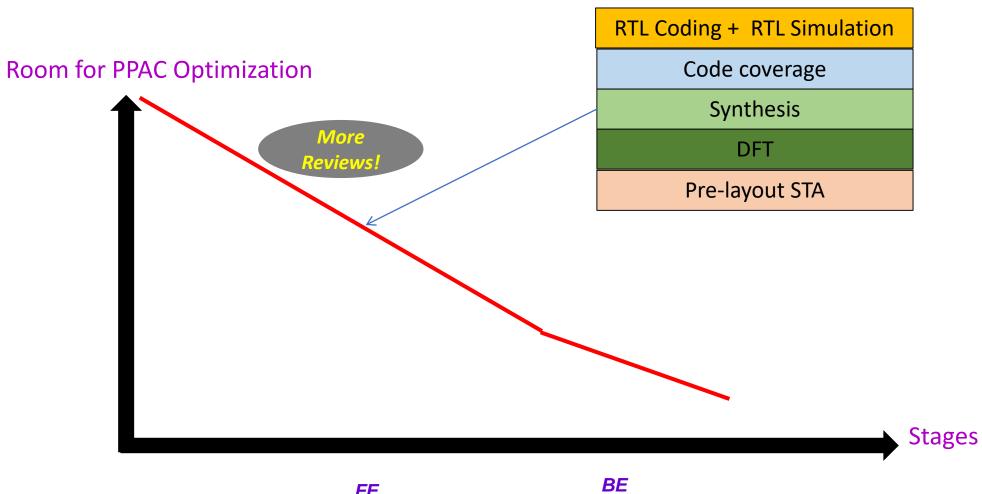

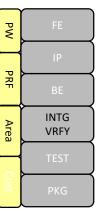

#### FE design with PPA space

FE

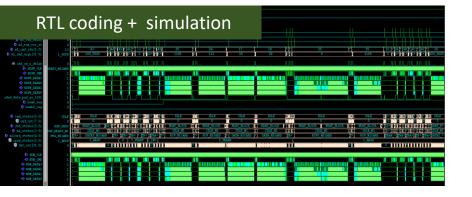

| (                                                                                                                                                                                                        | Code Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | overage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Help<br>N |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <ul> <li>dreader_top</li> <li>u_sdreader_tass</li> <li>u_sdreader_reg_r</li> <li>u_sdreader_rest_rev</li> <li>u_sdreader_rest_rev</li> <li>u_sdreader_cent_cent</li> <li>u_sdreader_cent_cent</li> </ul> | be<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block<br>block | 100% 04 / 40<br>100% 04 / 40<br>100% 04 / 40<br>100% 04 / 1000<br>20% 05% 05% 1000<br>05% 05% 05% 05%<br>05% 05% 05% 05%<br>05% 05% 05% 05%<br>05% 05% 05% 05%<br>05% 05% 05% 05%<br>05% 05% 05% 05%<br>05% 05% 05% 05% 05%<br>05% 05% 05% 05% 05%<br>05% 05% 05% 05% 05%<br>05% 05% 05% 05% 05% 05%<br>05% 05% 05% 05% 05% 05%<br>05% 05% 05% 05% 05% 05% 05%<br>05% 05% 05% 05% 05% 05% 05% 05% 05%<br>05% 05% 05% 05% 05% 05% 05% 05% 05% 05% | 04% (2007 / 3193)<br>84% (2007 / 3193)<br>76% (1192 / 1085)<br>94% (1192 / 1086)<br>94% (2017 / 336)<br>95% (2017 / 336)<br>90% (2017 / 336)<br>90% (2017 / 109)<br>90% (2000 / 100)<br>90% (200 |           |

| Summary [Code/Data] FSM J                                                                                                                                                                                | Functional ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W01013b38/TEMP/SDC2P0_CTRL_wadd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1751164751115175342 supplication task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Zest all  |

- MBIST => Self test Memory in the SOC.

- SCAN => Check connectivity between different flops in the design

- BSD => Test chip IO's interconnect.

#### Synthesis

- Check constrain is meet spec

- Good constrain is help performance

- review synthesis result (timing/power)

#### STAT/Timing Closure

- Review violation timing path

- Sizing /remove cell to meet timing spec

FE

#### Some of the consideration

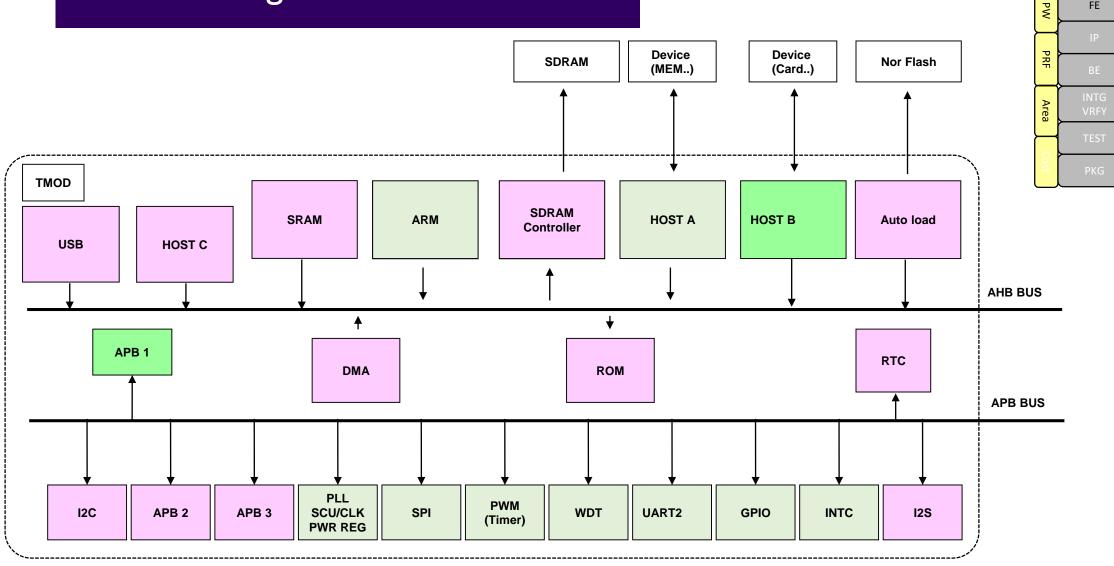

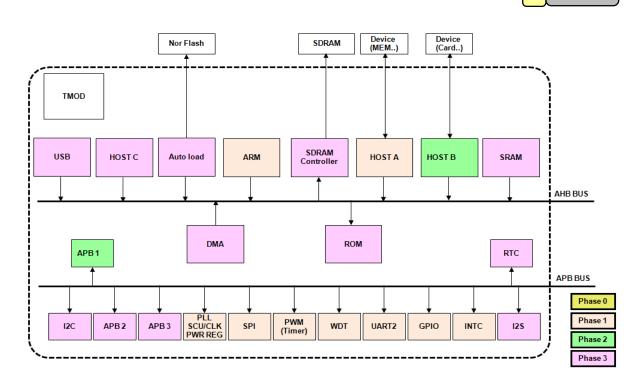

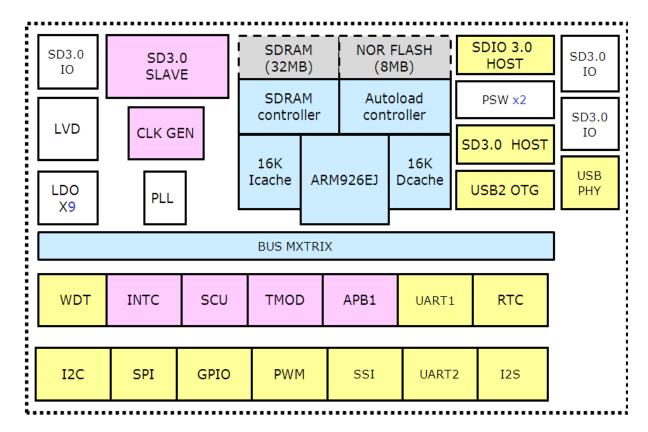

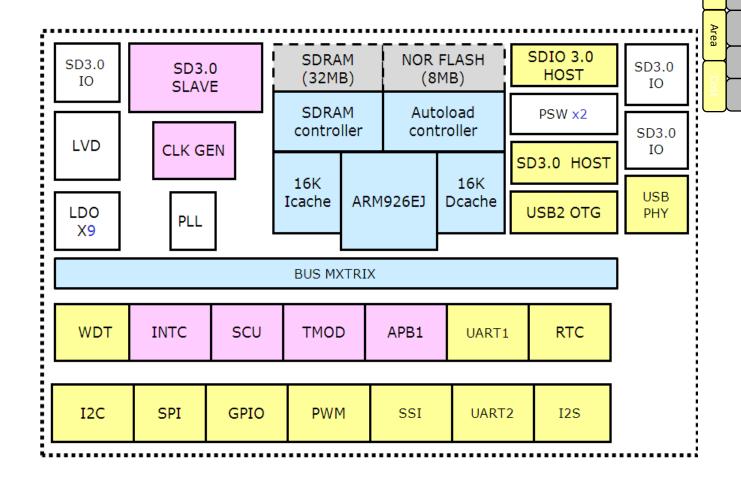

- SOC Arch

- Clock/Reset Arch

- Power Plan

- Memory usage

#### Design Architecture

FE

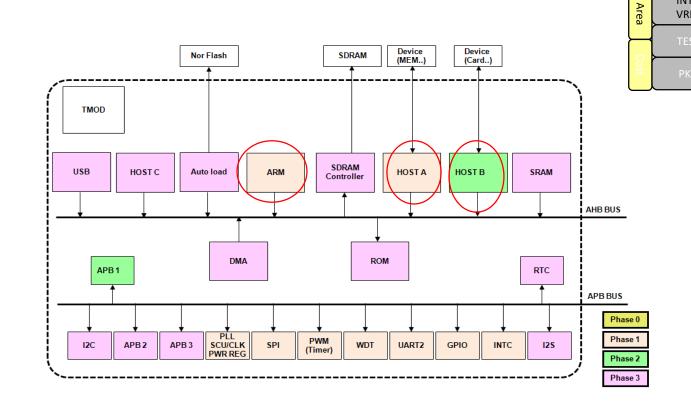

#### Scenario #1

- Performance issue at Host C .

- Host C is the AHB Slave, It is need SW to control the DMA access from HOST C to SDRAM.

- After analysis with it. We find SW is need spend 2 time move data form HOST C to DMA . DMA -> SDRAM. This performance is not good.

- After Optimization this arch. We modify the HOST C to AHB Master. It could direct access data to SDRAM by himself. It could reduce a lot of access time.

PRF

INTG VRFY

#### Scenario #1.2

- Check MBIST is work

- EX: ARM/HOST A/HOAT B have **MBIST** inside

- confirm these module could work success in function mode.

P₹

PRF

INTG

VRFY

#### CLK / RST

#### Some of the consideration

- Define Clock Arch for power save.

- Define Reset Arch

#### Scenario #2

- Review system power save plan

- Optimization RTL for Clock Gate

- Separate different operate mode for SW choose.

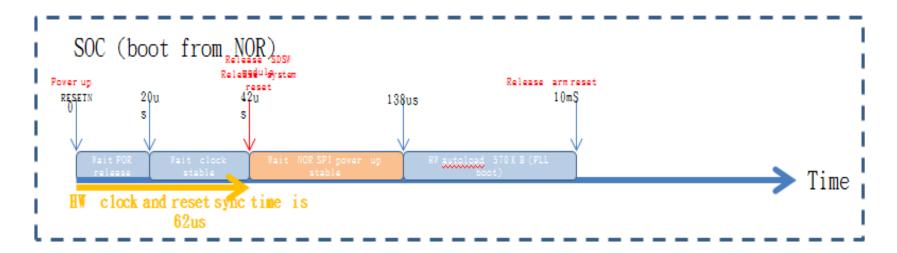

#### Boot Sequence

Things to consider in mind

- Define HW/SW Boot flow.

- Optimize Boot flow is meet timing/Power.

- Overall Boot time reduced

Š

PRF

Area

INTG

VRFY

#### Scenario #3

- Check HW/SW Boot flow.

- Review boot plan with timing and power.

- Optimize HW Boot flow.

- Confirm Boot flow is suit real application

#### Power Plan

# Design for Power

- Power saving plan

- Review IP/MEM usage

#### Scenario #3

- Review IP (Memory/PLL/LDO/IP) usage.

- Check real application timing/power limit

- Optimization suit IP usage status.

₽Ś

PRF

INTG

VRFY

#### Always think of how to improve PPA

#### Summary

- PPAC as the key index to measure how good a chip is Besides having the right knowledge & skillset

- FE is the area that you should design-in & optimize PPA the most in overall design execution

- Execute your flow with disciplines, always check back against PPAC at any stages!

## Thank You