## Calibre DRC, LVS and DFM overview

### Martin Niehoff

Application Engineer Calibre Manufacturing Solutions

January 2019

## Your Presenter – Martin Niehoff

- Graduation from Friedrich-Alexander University (Erlangen-Nürnberg, Germany):

- Major: Physics diploma thesis in experimental Optics

- Minor: Computer Science

- 1998 2004: Siemens Semiconductor / Infineon Technologies

- Metrology process engineering

- Lithography process engineering

- Lithography R&D (65nm & 45nm nodes)

- 2004 2010: Mentor Graphics

- European Product Specialist OPC & MDP

- 2010 2014: ASML/Brion

- Senior Application Engineer Fab Tools & OPC

- 2014 now: Mentor Graphics / Siemens

- European Application Engineer Calibre Manufacturing Solutions

#### Introduction

#### DRC, LVS, xRC:

- Calibre in the EDA Ecosystem

- Advanced Nodes

- Established Nodes

- Productivity

- Foundry Status

#### DFM:

- LFD

- YieldAnalyzer

- YieldEnhancer

#### Introduction

- DRC, LVS, xRC:

- Calibre in the EDA Ecosystem

- Advanced Nodes

- Established Nodes

- Productivity

- Foundry Status

- DFM:

- LFD

- YieldAnalyzer

- YieldEnhancer

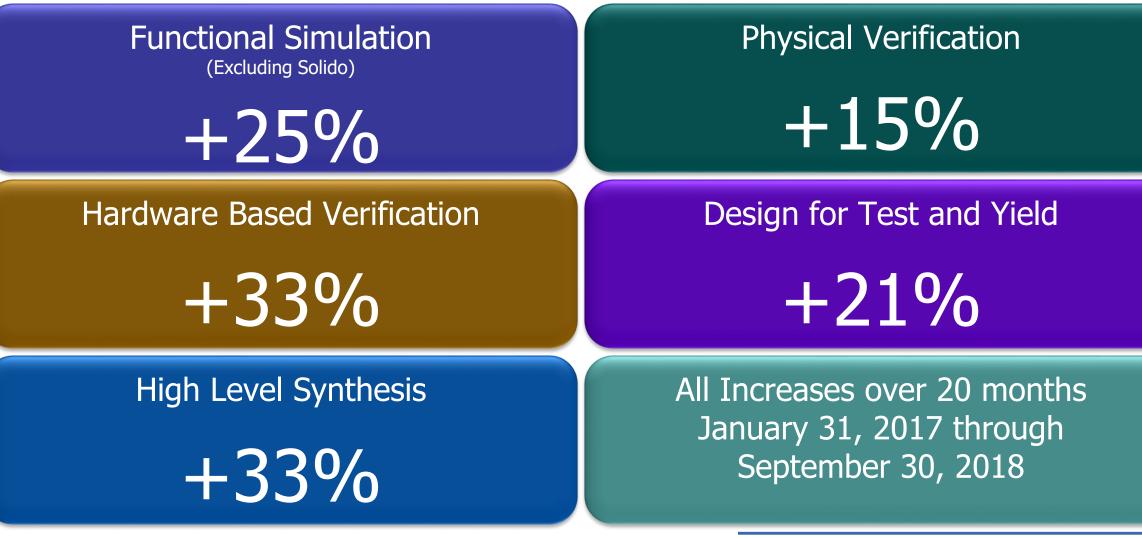

#### **Siemens Investing in Increasing R&D Headcount**

## DESIGN TO SILICON

#### Introduction

#### DRC, LVS, xRC:

#### - Calibre in the EDA Ecosystem

- Advanced Nodes

- Established Nodes

- Productivity

- Foundry Status

- DFM:

- LFD

- YieldAnalyzer

- YieldEnhancer

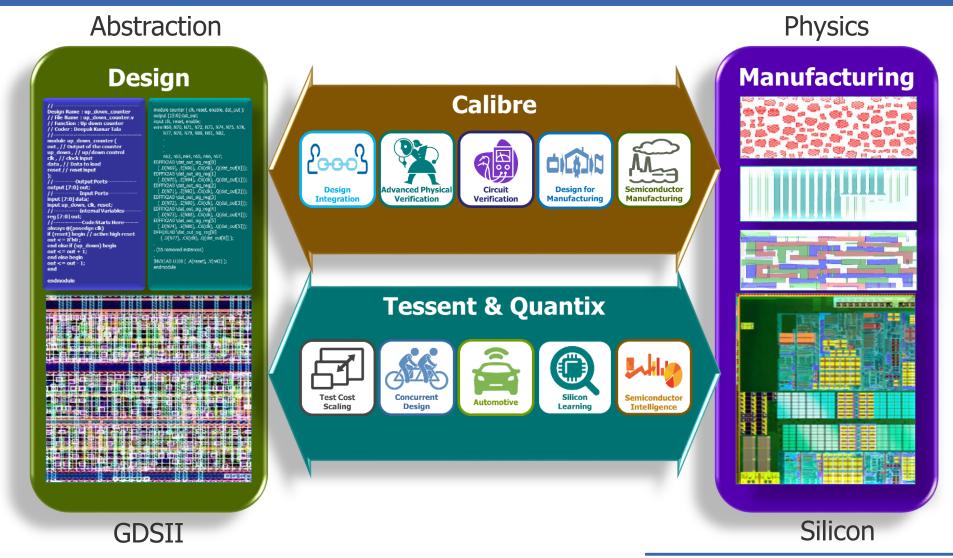

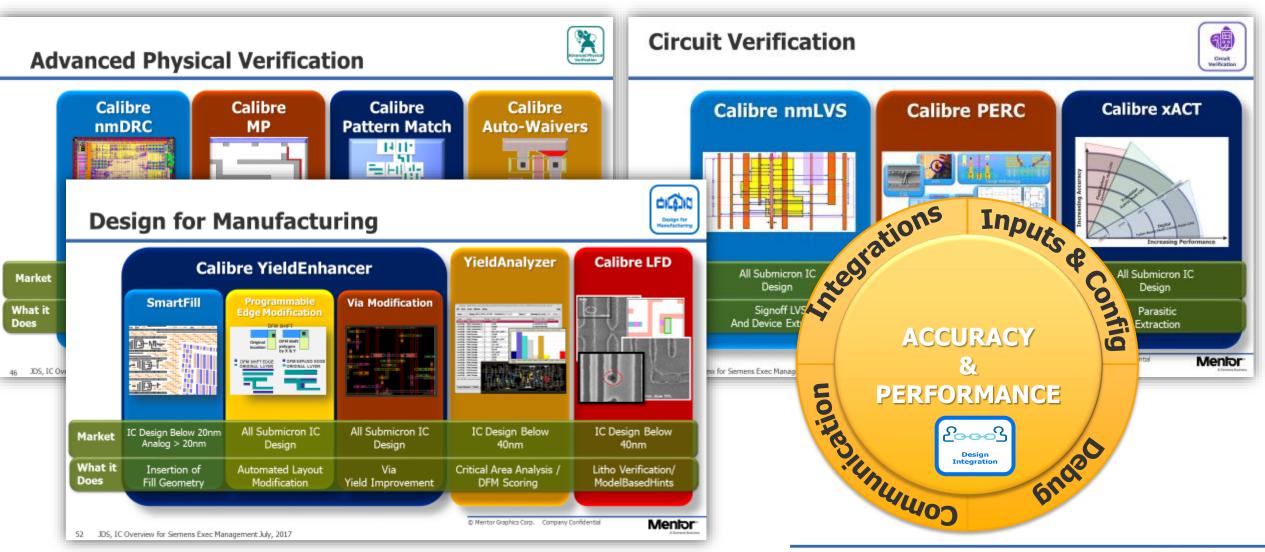

## **Calibre Design Solutions Portfolio**

Mento

A Siemens Busines

#### Introduction

#### DRC, LVS, xRC:

— Calibre in the EDA Ecosystem

#### — Advanced Nodes

- Established Nodes

- Productivity

- Foundry Status

#### DFM:

- LFD

- YieldAnalyzer

- YieldEnhancer

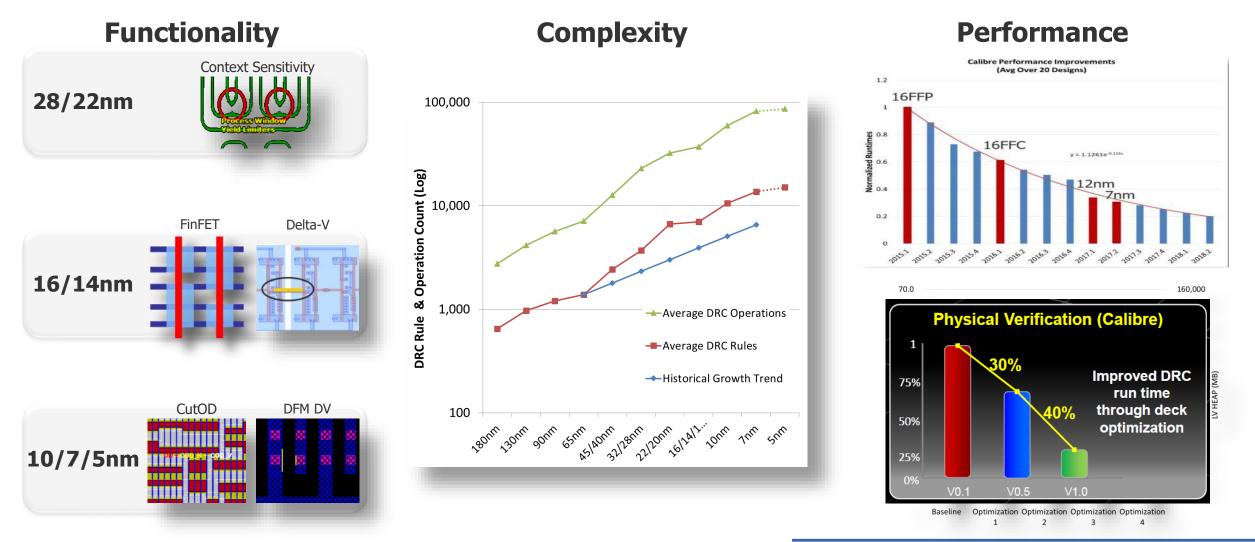

## Advanced Physical Verification

Men

A Siemens Busines

#### Introduction

- DRC, LVS, xRC:

- Calibre in the EDA Ecosystem

- Advanced Nodes

- Established Nodes

- Productivity

- Foundry Status

#### DFM:

- LFD

- YieldAnalyzer

- YieldEnhancer

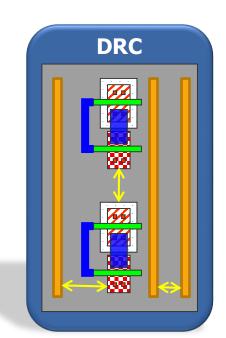

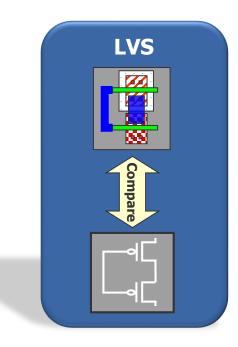

## **Traditional IC Verification**

## DRC, LVS, ERC

- Provide limited context, rules applied to entire design

- Often leverage "marker" / CAD layers to refine checking area

- Increased design complexity requires focused verification

## **TSMC ESD/Latch-up Rules – From Their DRM**

- "Un-checkable" with traditional EDA tools

- Includes reliability focused applications

Topology, P2P, CD, layout based latch-up

- Decks available for N28 and below

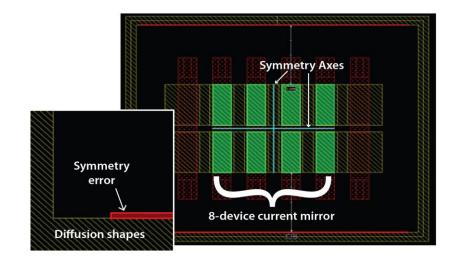

## **Analog Constraint Checking - RESCAR**

- Focused effort to improve reliability of automotive designs

- Developed through customer collaboration with Mentor for RESCAR project

- Includes checks for

- Alignment, Symmetry, Matched Orientation

- Parameter Match, Cluster, Others

- Simple constraint entry greatly simplifies adoption

- Jointly presented at DAC 2014 and ASP-DAC 2015

#### Introduction

- DRC, LVS, xRC:

- Calibre in the EDA Ecosystem

- Advanced Nodes

- Established Nodes

- Productivity

- Foundry Status

- DFM:

- LFD

- YieldAnalyzer

- YieldEnhancer

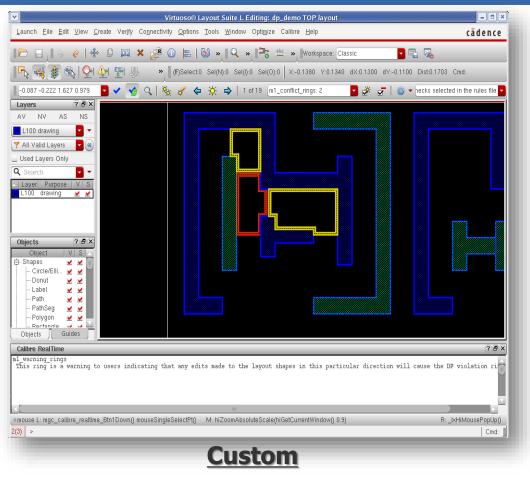

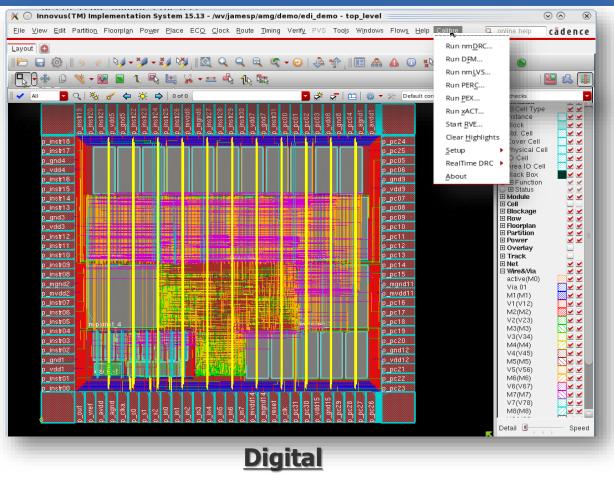

## **Calibre RealTime Platform: Accelerating DRC Closure**

Interactive checking during design creation

Manually fix "Last Few" errors <u>after</u> P&R

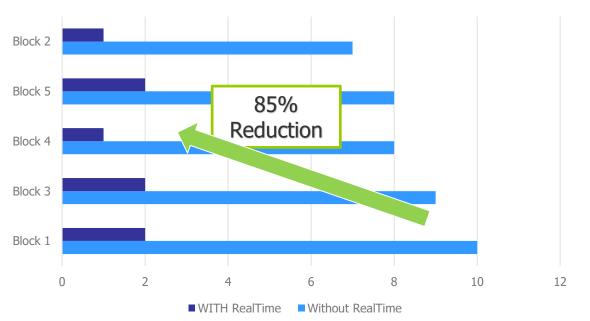

#### **Calibre RealTime Digital** Customer Results at Block Level

Block 3 Block 2 Block 1 0 1 2 3 4 5 6 7 8 9 With RealTime Without RealTime

Time to Reach DRC Clean Block

"40% reduction in DRC closure time for each block @ GF 22nm can save us *2 weeks to Tape-out* – *Invecas*  Time to Reach DRC Clean Block

"85% reduction in DRC fixing time for every block for every ECO for our 16nm design"

- Customer B

#### Introduction

- DRC, LVS, xRC:

- Calibre in the EDA Ecosystem

- Advanced Nodes

- Established Nodes

- Productivity

#### — Foundry Status

- DFM:

- LFD

- YieldAnalyzer

- YieldEnhancer

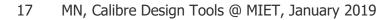

### **Calibre Process Support for Established Nodes**

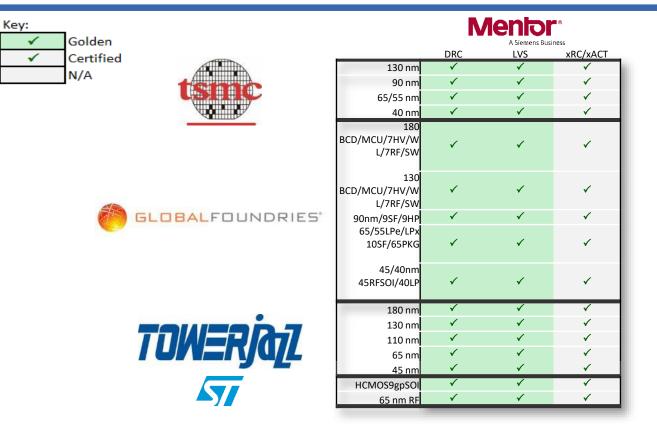

## Summary: Calibre is *The* Low Risk Choice

- TSMC Tech Symposium

- − N7: Will tape out  $\geq$ 50 chips in CY18

- Using Calibre: 49

- Calibre dominant at: Samsung, GF, UMC, SMIC, etc.

- Integrated everywhere

- Ecosystem

- Best in class EDA solutions

- Full solutions, others missing key tools:

- PERC

- SRAM/Pattern Matching

Source: Gary Smith EDA (December 2017)

#### Introduction

- DRC, LVS, xRC:

- Calibre in the EDA Ecosystem

- Advanced Nodes

- Established Nodes

- Productivity

- Foundry Status

#### DFM:

- LFD

- YieldAnalyzer

- YieldEnhancer

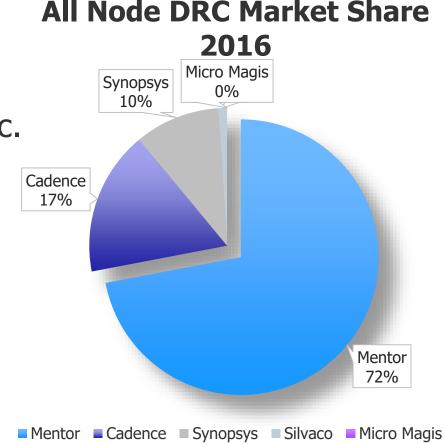

## **DFM Methodology**

#### Introduction

- DRC, LVS, xRC:

- Calibre in the EDA Ecosystem

- Advanced Nodes

- Established Nodes

- Productivity

- Foundry Status

- DFM:

- LFD

- YieldAnalyzer

- YieldEnhancer

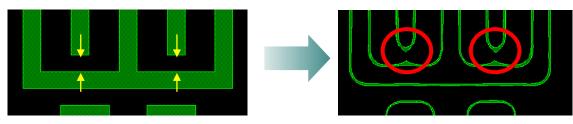

## **LFD vs DRC**

#### ■ DRC-clean $\neq$ printable

Courtesy of Luigi Capodieci, Ph.D. at AMD - SPIE Microlithography 2006

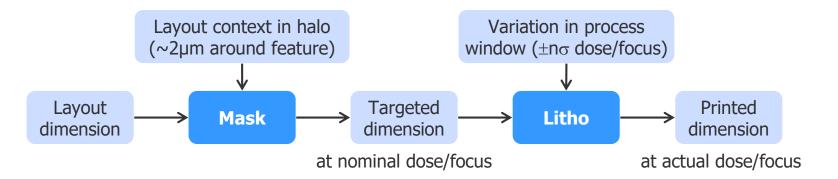

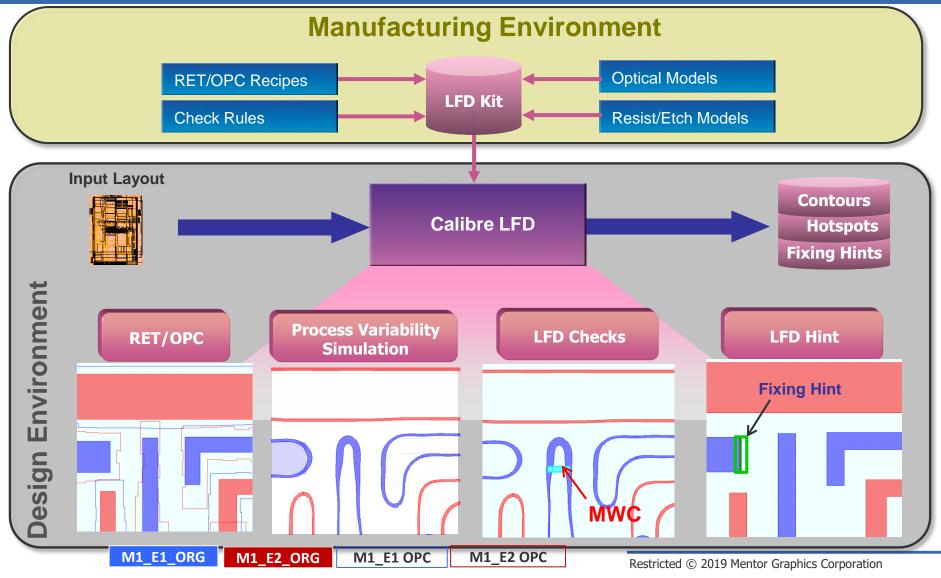

## Calibre® LFD: based on production RET/OPC recipes

#### Introduction

- DRC, LVS, xRC:

- Calibre in the EDA Ecosystem

- Advanced Nodes

- Established Nodes

- Productivity

- Foundry Status

- DFM:

- LFD

- YieldAnalyzer

- YieldEnhancer

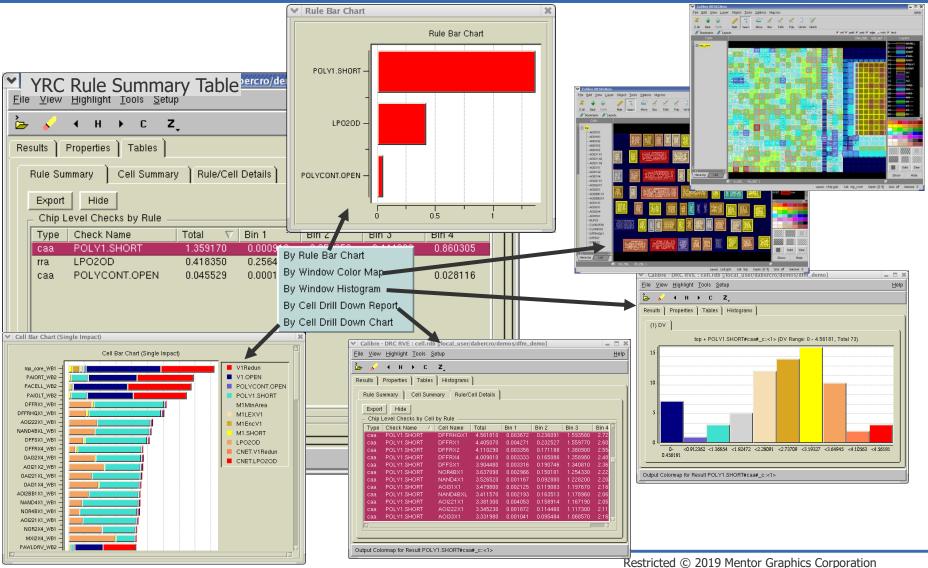

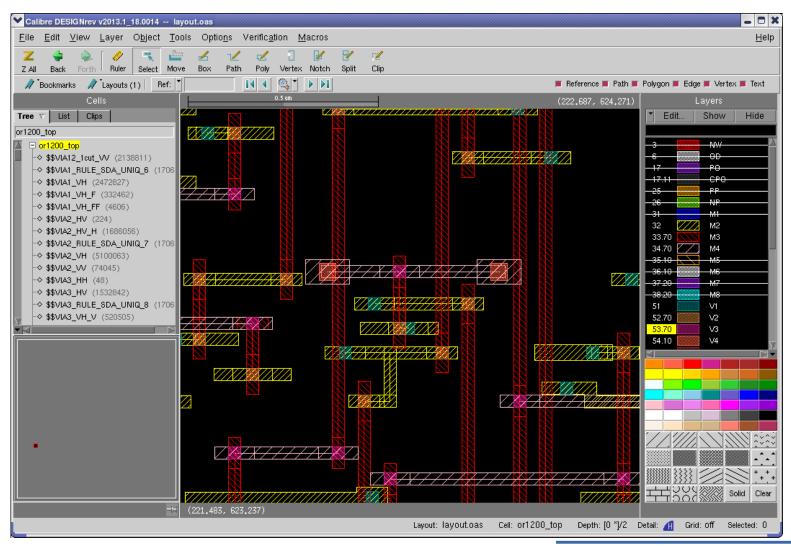

## **YieldAnalyzer Visualization**

#### Introduction

- DRC, LVS, xRC:

- Calibre in the EDA Ecosystem

- Advanced Nodes

- Established Nodes

- Productivity

- Foundry Status

#### DFM:

- LFD

- YieldAnalyzer

- YieldEnhancer

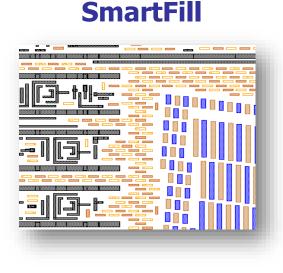

## A toolbox for layout modification

- Automatic or user-selected

- DRC-clean and DFM-aware

- Embedded and Programmable features

#### Programmable Edge Movement

#### Via enhancement

29

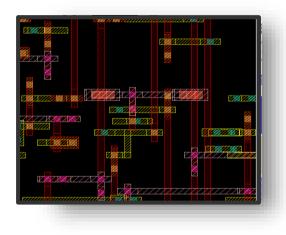

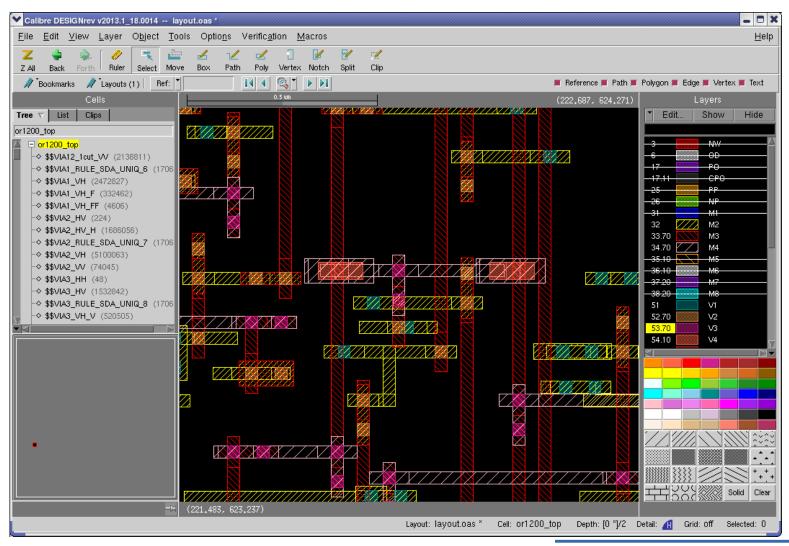

## **Screenshot before via insertion**

## **Screenshot after via insertion**

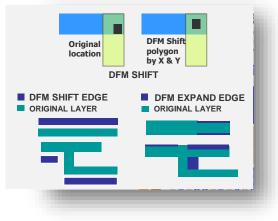

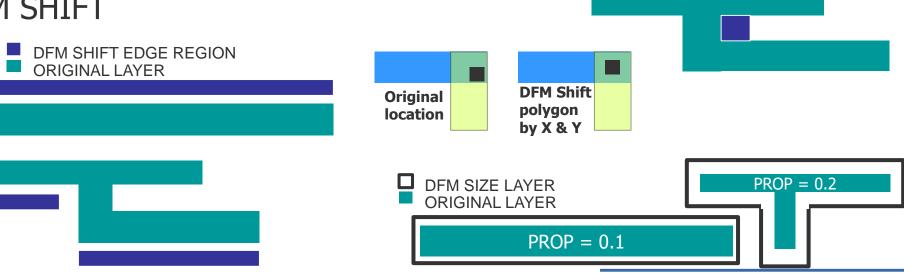

## Additional YieldEnhancer Commands: Programmable Edge Movement (PEM)

#### Requires deck development

- Users determine the required movement by analysis

- Manufacturing companies know from silicon results what changes are needed and by how much to improve Yield

DFM EXPAND EDGE FIX

- Released Property Based Edits

- DFM EXPAND EDGE, DFM GROW

- DFM SHIFT EDGE, DFM SIZE

- DFM SHIFT

**ORIGINAL LAYER WITH ISSUES**

# A Siemens Business

www.mentor.com