## Joseph A. Fisher • Paolo Faraboschi • Cliff Young

# Embedded Computing

A VLIW Approach to Architecture, Compilers, and Tools

## Praise for Embedded Computing: A VLIW Approach to Architecture, Compilers and Tools

There is little doubt that embedded computing is the new frontier of computer research. There is also a consensus that VLIW technology is extremely powerful in this domain. This book speaks with an authoritative voice on VLIW for embedded with true technical depth and deep wisdom from the pioneering experiences of the authors. This book will find a place on my shelf next to the classic texts on computer architecture and compiler optimization. It is simply that good.

Tom Conte Center for Embedded Systems Research, North Carolina State University

Written by one of the field's inventors with his collaborators, this book is the first complete exposition of the VLIW design philosophy for embedded systems. It can be read as a stand-alone reference on VLIW—a careful treatment of the ISA, compiling and program analysis tools needed to develop a new generation of embedded systems—or as a series of design case studies drawn from the authors' extensive experience. The authors' style is careful yet informal, and the book abounds with "flames," debunked "fallacies" and other material that engages the reader in the lively interplay between academic research and commercial development that has made this aspect of computer architecture so exciting. Embedded Computing: A VLIW Approach to Architecture, Compilers, and Tools will certainly be the definitive treatment of this important chapter in computer architecture.

Richard DeMillo Georgia Institute of Technology

This book does a superb job of laying down the foundations of VLIW computing and conveying how the VLIW principles have evolved to meet the needs of embedded computing. Due to the additional attention paid to characterizing a wide range of embedded applications and development of an accompanying toolchain, this book sets a new standard both as a reference and a text for embedded computing.

Rajiv Gupta The University of Arizona

A wealth of wisdom on a high-performance and power-efficient approach to embedded computing. I highly recommend it for both engineers and students.

Norm Jouppi HP Labs

Josh, Paolo, and Cliff have devoted most of their professional lives to developing and advancing the fundamental research and use of VLIW architectures and instruction level parallelism. They are also system-builders in the best and broadest sense of the term. This book offers deep insights into the field, and highlights the power of these technologies for use in the rapidly expanding field of high performance embedded computing. I believe this book will become required reading for anyone working in these technologies.

#### Dick Lampman HP Labs

Embedded Computing is a fabulous read, engagingly styled, with generous research and practical perspective, and authoritative, since Fisher has been responsible for this paradigm of simultaneously engineering the compiler and processor. Practicing engineers — both architects and embedded system designers — will find the techniques they will need to achieve the substantial benefits of VLIW-based systems. Instructors will value the rare juxtaposition of advanced technology with practical deployment examples, and students will enjoy the unusually interesting and mind-expanding chapter exercises.

Richard A. Lethin Reservoir Labs and Yale University

One of the strengths of this book is that it combines the perspectives of academic research, industrial development, as well as tool building. While its coverage of embedded architectures and compilers is very broad, it is also deep where necessary. Embedded Computing is a must-have for any student or practitioner of embedded computing.

Walid Najjar University of California, Riverside

## Embedded Computing

A VLIW Approach to Architecture, Compilers and Tools

TEAM LING – LIVE, INformative, Non-cost and Genuine !

# Embedded Computing

A VLIW Approach to Architecture, Compilers and Tools

Joseph A. Fisher Paolo Faraboschi Cliff Young

AMSTERDAM • BOSTON • HEIDELBERG • LONDON NEW YORK • OXFORD • PARIS • SAN DIEGO SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO Morgan Kaufmann is an imprint of Elsevier

| Publisher<br>Publishing Services Manager | Denise E. M. Penrose<br>Simon Crump  |

|------------------------------------------|--------------------------------------|

| Senior Production Editor                 | Angela Dooley                        |

| Editorial Assistant                      | Valerie Witte                        |

| Cover Design                             | Hannus Design                        |

| Cover Image                              | Santiago Calatrava's Alamillo Bridge |

| Text Design                              | Frances Baca Design                  |

| Composition                              | СЕРНА                                |

| Technical Illustration                   | Dartmouth Publishing                 |

| Copyeditor                               | Daril Bentley                        |

| Proofreader                              | Phyllis Coyne & Associates           |

| Indexer                                  | Northwind Editorial                  |

| Interior printer                         | The Maple-Vail Manufacturing Group   |

| Cover printer                            | Phoenix Color, Inc.                  |

Morgan Kaufmann Publishers is an imprint of Elsevier. 500 Sansome Street, Suite 400, San Francisco, CA 94111

This book is printed on acid-free paper.

© 2005 by Elsevier Inc. All rights reserved.

Designations used by companies to distinguish their products are often claimed as trademarks or registered trademarks. In all instances in which Morgan Kaufmann Publishers is aware of a claim, the product names appear in initial capital or all capital letters. Readers, however, should contact the appropriate companies for more complete information regarding trademarks and registration.

Cover image: Santiago Calatrava's Alamillo Bridge blends art and engineering to make architecture. While his design remains a modern, cable-stayed bridge, it simultaneously reinvents the category, breaking traditional assumptions and rearranging structural elements into a new form that is efficient, powerful, and beautiful. The authors chose this cover image for a number of reasons. Compiler engineering, which is at the heart of modern VLIW design, is similar to bridge engineering: both must be built to last for decades, to withstand changes in usage and replacement of components, and to weather much abuse. The VLIW design philosophy was one of the first computer architectural styles to bridge the software and hardware communities, treating them as equals and partners. And this book is meant as a bridge between the VLIW and embedded communities, which had historically been separate, but which today have complementary strengths and requirements.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means — electronic, mechanical, photocopying, scanning, or otherwise — without prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, e-mail: *permissions@elsevier.com.uk*. You may also complete your request on-line via the Elsevier homepage (*http://elsevier.com*) by selecting "Customer Support" and then "Obtaining Permissions."

ADVICE, PRAISE, AND ERRORS: Any correspondence related to this publication or intended for the authors should be addressed to FFY@VLIW.org. Information regarding error sightings is also encouraged and can be sent to mkp@mkp.com.

#### Library of Congress Cataloging-in-Publication Data

ISBN: 1-55860-766-8

For information on all Morgan Kaufmann publications, visit our Web site at www.mkp.com or www.books.elsevier.com.

Printed in the United States of America 04 05 06 07 08 5 4 3 2 1

To my wife Elizabeth, our children David and Dora, and my parents, Harry and the late Susan Fisher. And to my friend and mentor, Martin Davis. Josh Fisher

To the memory of my late parents Silvio and Gina, to my wife Tatiana and our daughter Silvia. Paolo Faraboschi

To the women of my family: Yueh-Jing, Dorothy, Matilda, Joyce, and Celeste. Cliff Young

To Bob Rau, a VLIW pioneer and true visionary, and a wonderful human being. We were privileged to know and work with him. **The Authors**

TEAM LING – LIVE, INformative, Non-cost and Genuine !

## About the Authors

**JOSEPH A. FISHER** is a Hewlett-Packard Senior Fellow at HP Labs, where he has worked since 1990 in instruction-level parallelism and in custom embedded VLIW processors and their compilers. Josh studied at the Courant Institute of NYU (B.A., M.A., and then Ph.D. in 1979), where he devised the trace scheduling compiler algorithm and coined the term *instruction-level parallelism*. As a professor at Yale University, he created and named VLIW architectures and invented many of the fundamental technologies of ILP. In 1984, he started Multiflow Computer with two members of his Yale team. Josh won an NSF Presidential Young Investigator Award in 1984, was the 1987 Connecticut Eli Whitney Entrepreneur of the Year, and in 2003 received the ACM/IEEE Eckert-Mauchly Award.

**PAOLO FARABOSCHI** is a Principal Research Scientist at HP Labs. Before joining Hewlett-Packard in 1994, Paolo received an M.S. (Laurea) and Ph.D. (Dottorato di Ricerca) in electrical engineering and computer science from the University of Genoa (Italy) in 1989 and 1993, respectively. His research interests skirt the boundary of hardware and software, including VLIW architectures, compilers, and embedded systems. More recently, he has been looking at the computing aspects of demanding content-processing applications. Paolo is an active member of the computer architecture community, has served in many program committees, and was Program Co-chair for MICRO (2001) and CASES (2003).

**CLIFF YOUNG** works for D. E. Shaw Research and Development, LLC, a member of the D. E. Shaw group of companies, on projects involving special-purpose, high-performance computers for computational biochemistry. Before his current position, he was a Member of Technical Staff at Bell Laboratories in Murray Hill, New Jersey. He received A.B., S.M., and Ph.D. degrees in computer science from Harvard University in 1989, 1995, and 1998, respectively.

TEAM LING – LIVE, INformative, Non-cost and Genuine !

# Foreword

Bob Colwell, R & E Colwell & Assoc. Inc.

here are two ways to learn more about your country: you can study it directly by traveling around in it or you can study it indirectly by leaving it. The first method yields facts and insights directly in context, and the second by contrast. Our tradition in computer engineering has been to seldom leave our neighborhood. If you want to learn about operating systems, you read an OS book. For multiprocessor systems, you get a book that maps out the MP space.

The book you are holding in your hands can serve admirably in that direct sense. If the technology you are working on is associated with VLIWs or "embedded computing," clearly it is imperative that you read this book.

But what pleasantly surprised me was how useful this book is, even if one's work is not VLIW-related or has no obvious relationship to embedded computing. I had long felt it was time for Josh Fisher to write his magnum opus on VLIWs, so when I first heard that he and his coauthors were working on a book with VLIW in the title I naturally and enthusiastically assumed this was it. Then I heard the words "embedded computing" were also in the title and felt considerable uncertainty, having spent most of my professional career in the general-purpose computing arena. I thought embedded computing was interesting, but mostly in the same sense that studying cosmology was interesting: intellectually challenging, but what does it have to do with me?

I should have known better. I don't think Josh Fisher can write boring text. He doesn't know how. (I still consider his "Very Long Instruction Word Architectures and the ELI-512" paper from ISCA-10 to be the finest conference publication I have ever read.) And he seems to have either found like-minded coauthors in Faraboschi and Young or has taught them well, because *Embedded Computing: A VLIW Approach to Architecture, Tools and Compilers* is enthralling in its clarity and exhilarating in its scope. If you are involved in computer system design or programming, you must still read this book, because it will take you to places where the views are spectacular, including those looking over to where you usually live. You don't necessarily have to agree with every point the authors make, but you *will* understand what they are trying to say, and they *will* make you think.

One of the best legacies of the classic Hennessy and Patterson computer architecture textbooks is that the success of their format and style has encouraged more books like theirs. In *Embedded Computing: A VLIW Approach to Architecture, Tools and Compilers*, you will find the pitfalls, controversies, and occasional opinion sidebars that made

H&P such a joy to read. This kind of technical exposition is like vulcanology done while standing on an active volcano. Look over there, and see molten lava running under a new fissure in the rocks. Feel the heat; it commands your full attention. It's immersive, it's interesting, and it's immediate. If your Vibram soles start melting, it's still worth it. You probably needed new shoes anyway.

I first met Josh when I was a grad student at Carnegie-Mellon in 1982. He spent an hour earnestly describing to me how a sufficiently talented compiler could in principle find enough parallelism, via a technique he called trace scheduling, to keep a really wild-looking hardware engine busy. The compiler would speculatively move code all over the place, and then invent more code to fix up what it got wrong. I thought to myself "So *this* is what a lunatic looks like up close. I hope he's not dangerous." Two years later I joined him at Multiflow and learned more in the next five years than I ever have, before or since.

It was an honor to review an early draft of this book, and I was thrilled to be asked to contribute this foreword. As the book makes clear, general-purpose computing has traditionally gotten the glory, while embedded computing quietly keeps our infrastructure running. This is probably just a sign of the immaturity of the general-purpose computing environment (even though we "nonembedded" types don't like to admit that). With general-purpose computers, people "use the computer" to do something. But with embedded computers, people accomplish some task, blithely and happily unaware that there's a computer involved. Indeed, if they had to be conscious of the computer, their embedded computers would have already failed: antilock brakes and engine controllers, for instance. General-purpose CPUs have a few microarchitecture performance tricks to show their embedded brethren, but the embedded space has much more to teach the general computing folks about the bigger picture: total cost of ownership, who lives in the adjacent neighborhoods, and what they need for all to live harmoniously. This book is a wonderful contribution toward that evolution.

# Contents

| About the Authors                                                                                                        | ix             |

|--------------------------------------------------------------------------------------------------------------------------|----------------|

| Foreword                                                                                                                 | xi             |

| Preface xxx                                                                                                              | vii            |

| Content and StructurexxvThe VEX (VLIW Example) Computing SystemxxAudiencexxCross-cutting TopicsxxHow to Read This Bookxx | xx<br>xx<br>xi |

| Figure Acknowledgmentsxxx                                                                                                | iv             |

| Acknowledgmentsxx                                                                                                        | xv             |

| An  | Introdu | action to Embedded Processing                          | 1  |

|-----|---------|--------------------------------------------------------|----|

| 1.1 | What Is | Embedded Computing?                                    | З  |

|     | 1.1.1   | Attributes of Embedded Devices                         | 4  |

|     | 1.1.2   | Embedded Is Growing                                    | 5  |

| 1.2 | Disting | uishing Between Embedded and General-Purpose Computing | 6  |

|     | 1.2.1   | The "Run One Program Only" Phenomenon                  | 8  |

|     | 1.2.2   | Backward and Binary Compatibility                      | g  |

|     | 1.2.3   | Physical Limits in the Embedded Domain                 | 10 |

| 1.3 | Charact | erizing Embedded Computing                             | 11 |

|     | 1.3.1   | Categorization by Type of Processing Engine            | 12 |

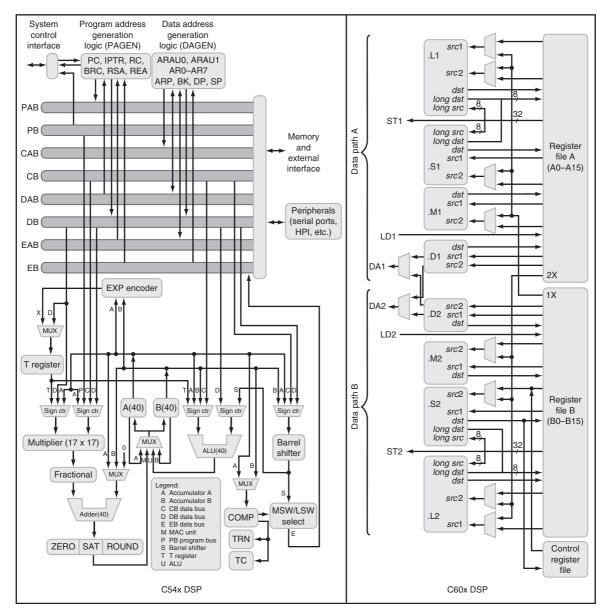

|     |         | Digital Signal Processors                              | 13 |

|     |         | Network Processors                                     | 16 |

|     | 1.3.2   | Categorization by Application Area                     | 17 |

|     |         | The Image Processing and Consumer Market               | 18 |

|     |         | The Communications Market                              | 20 |

|     |         | The Automotive Market                                  | 22 |

|     | 1.3.3   | Categorization by Workload Differences                 | 22 |

| 1.4 | Embedd  | led Market Structure                                   | 23 |

|     | 1.4.1   | The Market for Embedded Processor Cores                | 24 |

|     | 1.4.2   | Business Model of Embedded Processors     | 25 |

|-----|---------|-------------------------------------------|----|

|     | 1.4.3   | Costs and Product Volume                  | 26 |

|     | 1.4.4   | Software and the Embedded Software Market | 28 |

|     | 1.4.5   | Industry Standards                        | 28 |

|     | 1.4.6   | Product Life Cycle                        | 30 |

|     | 1.4.7   | The Transition to SoC Design              | 31 |

|     |         | Effects of SoC on the Business Model      | 34 |

|     |         | Centers of Embedded Design                | 35 |

|     | 1.4.8   | The Future of Embedded Systems            | 36 |

|     |         | Connectivity: Always-on Infrastructure    | 36 |

|     |         | State: Personal Storage                   | 36 |

|     |         | Administration                            | 37 |

|     |         | Security                                  | 37 |

|     |         | The Next Generation                       | 37 |

| 1.5 | Further | r Reading                                 | 38 |

| 1.6 |         | es                                        | 40 |

| An  | Overv   | iew of VLIW and ILP                                 | 45 |

|-----|---------|-----------------------------------------------------|----|

| 2.1 | Semant  | tics and Parallelism                                | 46 |

|     | 2.1.1   | Baseline: Sequential Program Semantics              | 46 |

|     | 2.1.2   | Pipelined Execution, Overlapped Execution, and      |    |

|     |         | Multiple Execution Units                            | 47 |

|     | 2.1.3   | Dependence and Program Rearrangement                | 51 |

|     | 2.1.4   | ILP and Other Forms of Parallelism                  | 52 |

| 2.2 | Design  | Philosophies                                        | 54 |

|     | 2.2.1   | An Illustration of Design Philosophies: RISC        |    |

|     |         | Versus CISC                                         | 56 |

|     | 2.2.2   | First Definition of VLIW                            | 57 |

|     | 2.2.3   | A Design Philosophy: VLIW                           | 59 |

|     |         | VLIW Versus Superscalar                             | 59 |

|     |         | VLIW Versus DSP                                     | 62 |

| 2.3 | Role of | the Compiler                                        | 63 |

|     | 2.3.1   | The Phases of a High-Performance Compiler           | 63 |

|     | 2.3.2   | Compiling for ILP and VLIW                          | 65 |

| 2.4 | VLIW i  | n the Embedded and DSP Domains                      | 69 |

| 2.5 | Histori | cal Perspective and Further Reading                 | 71 |

|     | 2.5.1   | ILP Hardware in the 1960s and 1970s                 | 71 |

|     |         | Early Supercomputer Arithmetic Units                | 71 |

|     |         | Attached Signal Processors                          | 72 |

|     |         | Horizontal Microcode                                | 72 |

|     | 2.5.2   | The Development of ILP Code Generation in the 1980s | 73 |

|     |         | Acyclic Microcode Compaction Techniques             | 73 |

|     |         | Cyclic Techniques: Software Pipelining              | 75 |

|     | 2.5.3   | VLIW Development in the 1980s | 76 |

|-----|---------|-------------------------------|----|

|     | 2.5.4   | ILP in the 1990s and 2000s    | 77 |

| 2.6 | Exercis | es                            | 78 |

| An  | Overview of ISA Design                               | 83  |

|-----|------------------------------------------------------|-----|

| 3.1 | Overview: What to Hide                               | 84  |

|     | 3.1.1 Architectural State: Memory and Registers      | 84  |

|     | 3.1.2 Pipelining and Operational Latency             | 85  |

|     | 3.1.3 Multiple Issue and Hazards                     | 86  |

|     | Exposing Dependence and Independence                 | 86  |

|     | Structural Hazards                                   | 87  |

|     | Resource Hazards                                     | 89  |

|     | 3.1.4 Exception and Interrupt Handling               | 89  |

|     | 3.1.5 Discussion                                     | 90  |

| 3.2 | Basic VLIW Design Principles                         | 91  |

|     | 3.2.1 Implications for Compilers and Implementations | 92  |

|     | 3.2.2 Execution Model Subtleties                     | 93  |

| 3.3 | Designing a VLIW ISA for Embedded Systems            | 95  |

|     | 3.3.1 Application Domain                             | 96  |

|     | 3.3.2 ILP Style                                      | 98  |

|     | 3.3.3 Hardware/Software Tradeoffs                    | 100 |

| 3.4 | Instruction-set Encoding                             | 101 |

|     | 3.4.1 A Larger Definition of Architecture            | 101 |

|     | 3.4.2 Encoding and Architectural Style               | 105 |

|     | RISC Encodings                                       | 107 |

|     | CISC Encodings                                       | 108 |

|     | VLIW Encodings                                       | 109 |

|     | Why Not Superscalar Encodings?                       | 109 |

|     | DSP Encodings                                        | 110 |

|     | Vector Encodings                                     | 111 |

| 3.5 | VLIW Encoding                                        | 112 |

|     |                                                      | 113 |

|     | 3.5.2 Instruction Encoding                           | 113 |

|     | Fixed-overhead Encoding                              | 115 |

|     | Distributed Encoding                                 | 115 |

|     | -                                                    | 116 |

|     |                                                      | 117 |

| 3.6 |                                                      | 119 |

| 3.7 | 0                                                    | 121 |

| 3.8 | Exercises                                            | 121 |

|     |                                                      |     |

| Arc | hitectu | ıral Structures in ISA Design                   | 125 |

|-----|---------|-------------------------------------------------|-----|

| 4.1 | The Da  | tapath                                          | 127 |

|     | 4.1.1   | Location of Operands and Results                | 127 |

|     | 4.1.2   | Datapath Width                                  | 127 |

|     | 4.1.3   | Operation Repertoire                            | 129 |

|     |         | Simple Integer and Compare Operations           | 131 |

|     |         | Carry, Overflow, and Other Flags                | 131 |

|     |         | Common Bitwise Utilities                        | 132 |

|     |         | Integer Multiplication                          | 132 |

|     |         | Fixed-point Multiplication                      | 133 |

|     |         | Integer Division                                | 135 |

|     |         | Floating-point Operations                       | 136 |

|     |         | Saturated Arithmetic                            | 137 |

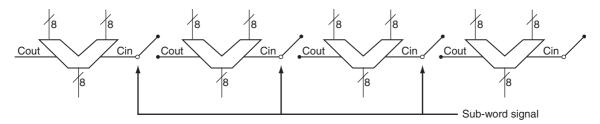

|     | 4.1.4   | Micro-SIMD Operations                           | 139 |

|     |         | Alignment Issues                                | 141 |

|     |         | Precision Issues                                | 141 |

|     |         | Dealing with Control Flow                       | 142 |

|     |         | Pack, Unpack, and Mix                           | 143 |

|     |         | Reductions                                      | 143 |

|     | 4.1.5   | Constants                                       | 144 |

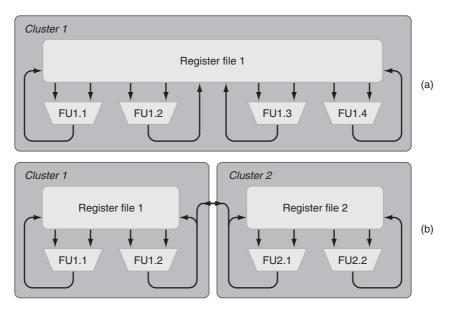

| 4.2 | Registe | rs and Clusters                                 | 144 |

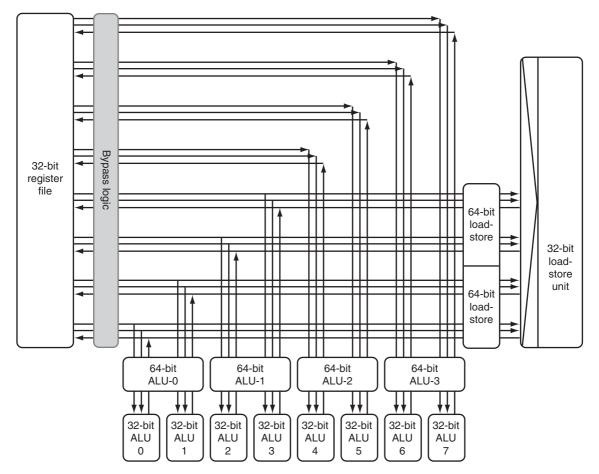

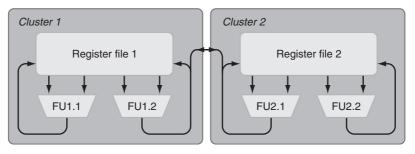

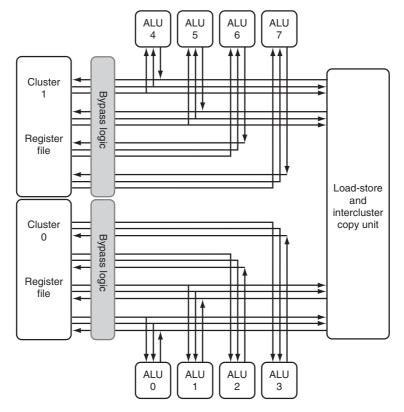

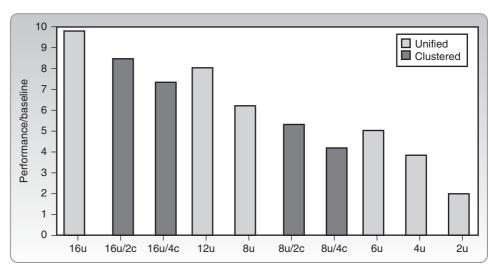

|     | 4.2.1   | Clustering                                      | 145 |

|     |         | Architecturally Invisible Clustering            | 147 |

|     |         | Architecturally Visible Clustering              | 147 |

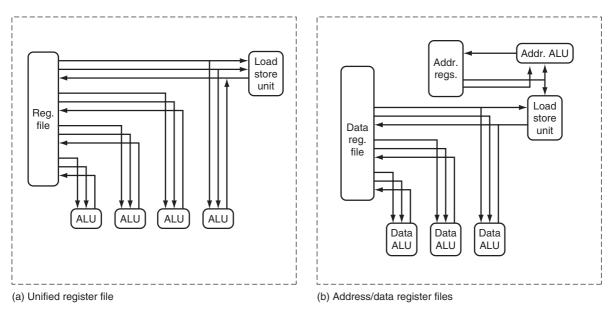

|     | 4.2.2   | Heterogeneous Register Files                    | 149 |

|     | 4.2.3   | Address and Data Registers                      | 149 |

|     | 4.2.4   | Special Register File Features                  | 150 |

|     |         | Indexed Register Files                          | 150 |

|     |         | Rotating Register Files                         | 151 |

| 4.3 | Memor   | y Architecture                                  | 151 |

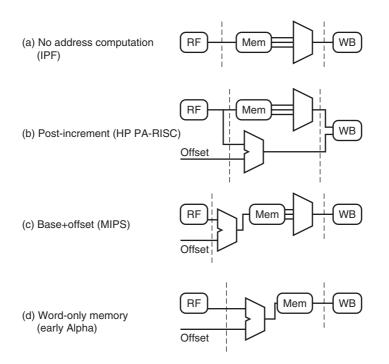

|     | 4.3.1   | Addressing Modes                                | 152 |

|     | 4.3.2   | Access Sizes                                    | 153 |

|     | 4.3.3   | Alignment Issues                                | 153 |

|     | 4.3.4   | Caches and Local Memories                       | 154 |

|     |         | Prefetching                                     | 154 |

|     |         | Local Memories and Lockable Caches              | 156 |

|     | 4.3.5   | Exotic Addressing Modes for Embedded Processing | 156 |

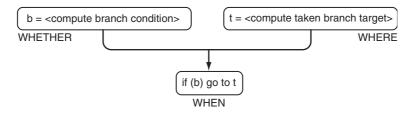

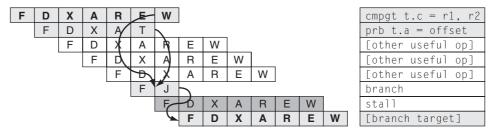

| 4.4 | Branch  | Architecture                                    | 156 |

|     | 4.4.1   | Unbundling Branches                             | 158 |

|     |         | Two-step Branching                              | 159 |

|     |         | Three-step Branching                            | 159 |

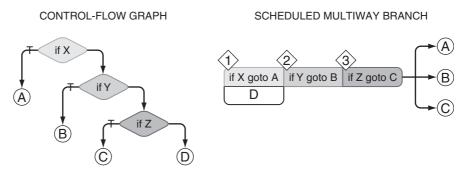

|     | 4.4.2   | Multiway Branches                               | 160 |

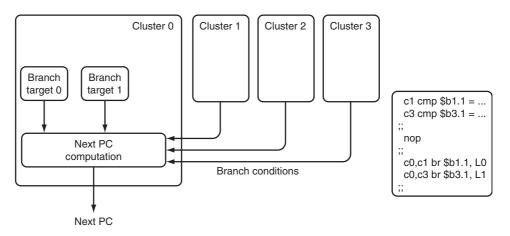

|     | 4.4.3   | Multicluster Branches              | 161 |

|-----|---------|------------------------------------|-----|

|     | 4.4.4   | Branches and Loops                 | 162 |

| 4.5 | Specula | ation and Predication              | 163 |

|     | 4.5.1   | Speculation                        | 163 |

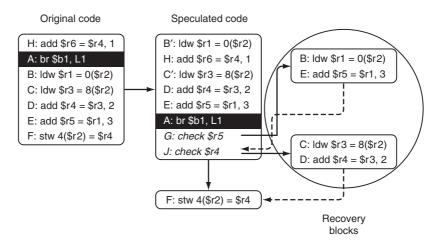

|     |         | Control Speculation                | 164 |

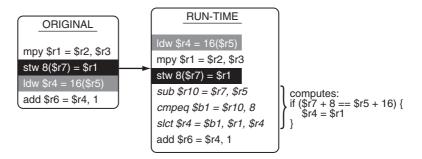

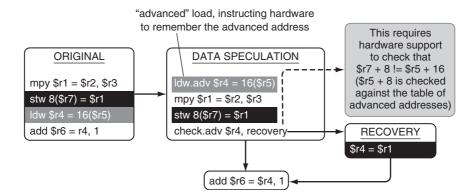

|     |         | Data Speculation                   | 167 |

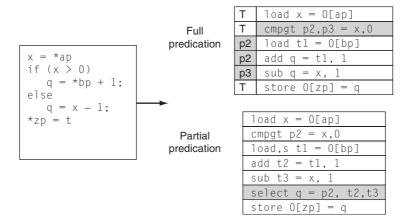

|     | 4.5.2   | Predication                        | 168 |

|     |         | Full Predication                   | 169 |

|     |         | Partial Predication                | 170 |

|     |         | Cost and Benefits of Predication   | 171 |

|     |         | Predication in the Embedded Domain | 172 |

| 4.6 |         | Operations                         | 173 |

| 4.7 | Further | Reading                            | 174 |

| 4.8 | Exercis | es                                 | 175 |

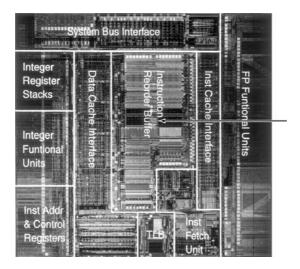

| Mic | roarch   | itecture Design                              | 179 |

|-----|----------|----------------------------------------------|-----|

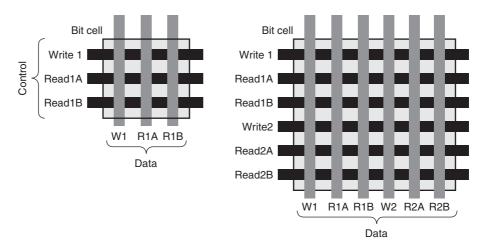

| 5.1 | Register | r File Design                                | 182 |

|     | 5.1.1    | Register File Structure                      | 182 |

|     | 5.1.2    | Register Files, Technology, and Clustering   | 183 |

|     | 5.1.3    | Separate Address and Data Register Files     | 184 |

|     | 5.1.4    | Special Registers and Register File Features | 186 |

| 5.2 | Pipeline | e Design                                     | 186 |

|     | 5.2.1    | Balancing a Pipeline                         | 187 |

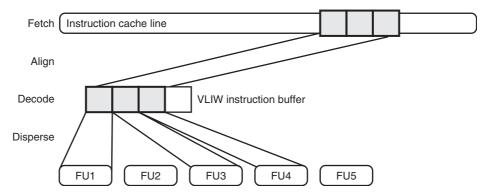

| 5.3 | VLIW F   | etch, Sequencing, and Decoding               | 191 |

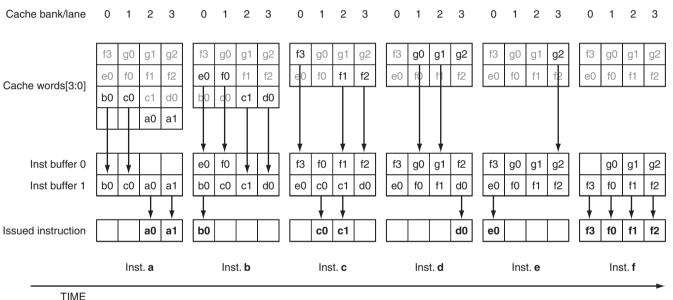

|     | 5.3.1    | Instruction Fetch                            | 191 |

|     | 5.3.2    | Alignment and Instruction Length             | 192 |

|     | 5.3.3    | Decoding and Dispersal                       | 194 |

|     | 5.3.4    | Decoding and ISA Extensions                  | 195 |

| 5.4 | The Dat  | apath                                        | 195 |

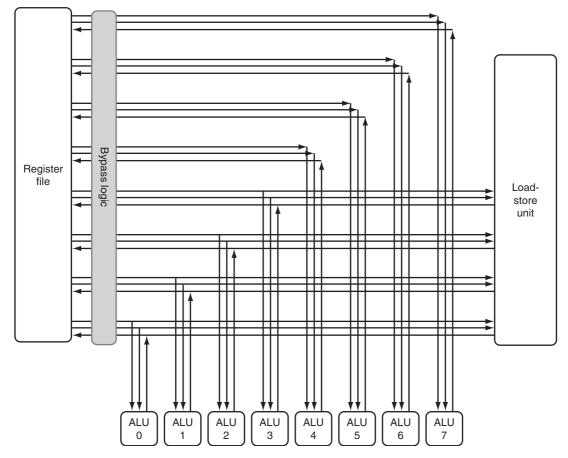

|     | 5.4.1    | Execution Units                              | 197 |

|     | 5.4.2    | Bypassing and Forwarding Logic               | 200 |

|     | 5.4.3    | Exposing Latencies                           | 202 |

|     | 5.4.4    | Predication and Selects                      | 204 |

| 5.5 | Memory   | y Architecture                               | 206 |

|     | 5.5.1    | Local Memory and Caches                      | 206 |

|     | 5.5.2    | Byte Manipulation                            | 209 |

|     | 5.5.3    | Addressing, Protection, and Virtual Memory   | 210 |

|     | 5.5.4    | Memories in Multiprocessor Systems           | 211 |

|     | 5.5.5    | Memory Speculation                           | 213 |

| 5.6 | The Co   | ntrol Unit                                   | 214 |

|     | 5.6.1    | Branch Architecture                          | 214 |

|     | 5.6.2    | Predication and Selects                      | 215 |

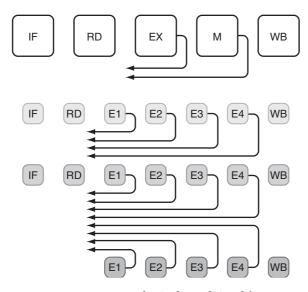

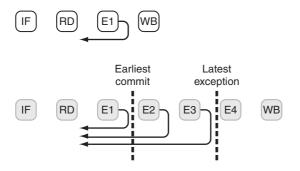

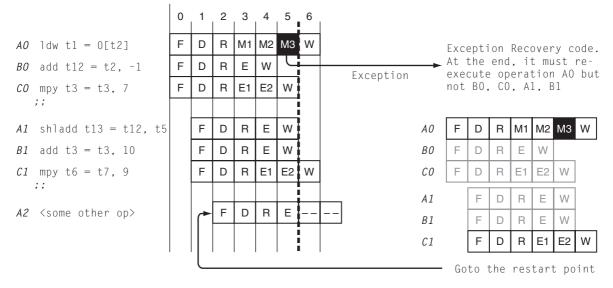

|      | 5.6.3    | Interrupts and Exceptions         | 216 |

|------|----------|-----------------------------------|-----|

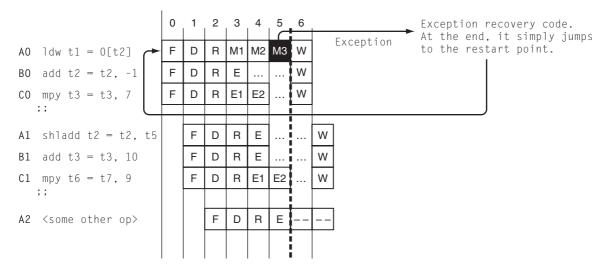

|      | 5.6.4    | Exceptions and Pipelining         | 218 |

|      |          | Drain and Flush Pipeline Models   | 218 |

|      |          | Early Commit                      | 219 |

|      |          | Delayed Commit                    | 220 |

| 5.7  | Control  | Registers                         | 221 |

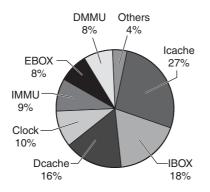

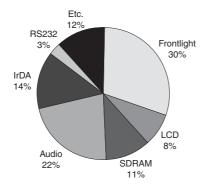

| 5.8  | Power C  | Considerations                    | 221 |

|      | 5.8.1    | Energy Efficiency and ILP         | 222 |

|      |          | System-level Power Considerations | 224 |

| 5.9  | Further  | Reading                           | 225 |

| 5.10 | Exercise | 98                                | 227 |

| Sys | tem De  | esign and Simulation                                | 231 |

|-----|---------|-----------------------------------------------------|-----|

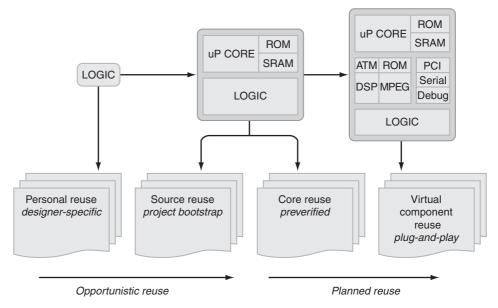

| 6.1 | System  | -on-a-Chip (SoC)                                    | 231 |

|     | 6.1.1   | IP Blocks and Design Reuse                          | 232 |

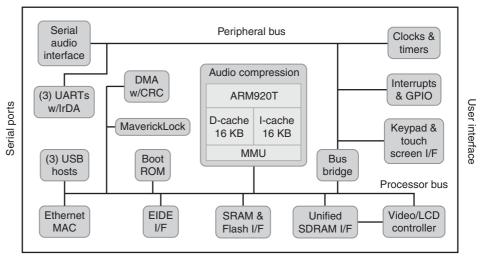

|     |         | A Concrete SoC Example                              | 233 |

|     |         | Virtual Components and the VSIA Alliance            | 235 |

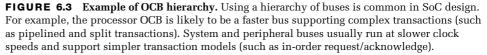

|     | 6.1.2   | Design Flows                                        | 236 |

|     |         | Creation Flow                                       | 236 |

|     |         | Verification Flow                                   | 238 |

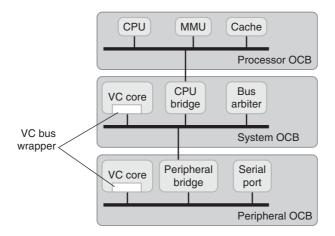

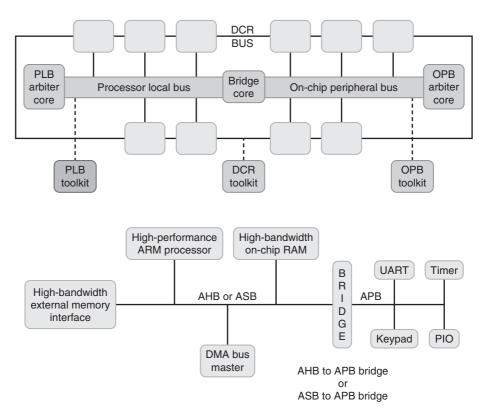

|     | 6.1.3   | SoC Buses                                           | 239 |

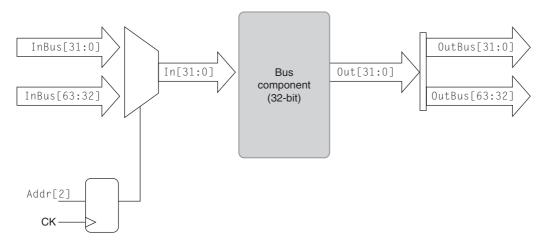

|     |         | Data Widths                                         | 240 |

|     |         | Masters, Slaves, and Arbiters                       | 241 |

|     |         | Bus Transactions                                    | 242 |

|     |         | Test Modes                                          | 244 |

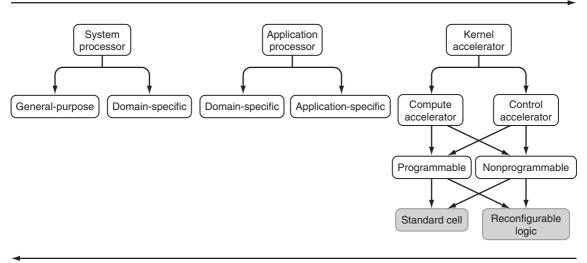

| 6.2 | Process | or Cores and SoC                                    | 245 |

|     | 6.2.1   | Nonprogrammable Accelerators                        | 246 |

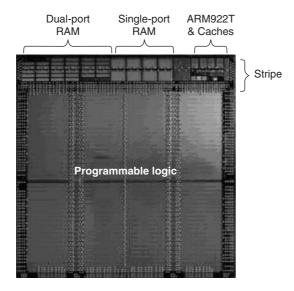

|     |         | Reconfigurable Logic                                | 248 |

|     | 6.2.2   | Multiprocessing on a Chip                           | 250 |

|     |         | Symmetric Multiprocessing                           | 250 |

|     |         | Heterogeneous Multiprocessing                       | 251 |

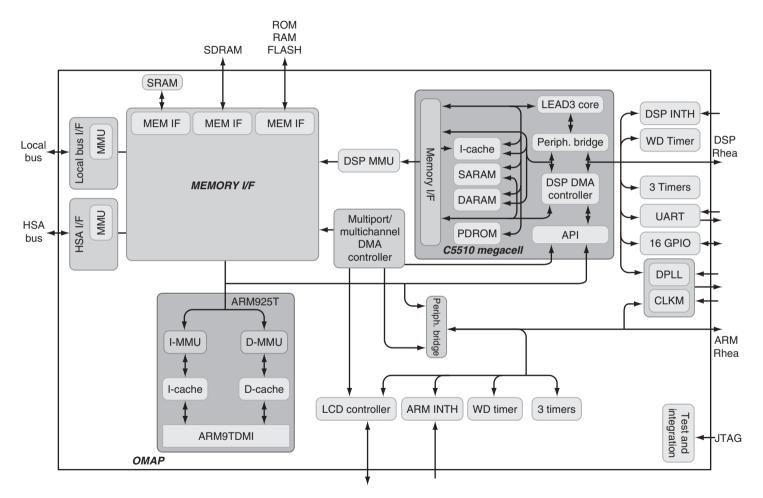

|     |         | Example: A Multicore Platform for Mobile Multimedia | 252 |

| 6.3 | Overvie | ew of Simulation                                    | 254 |

|     | 6.3.1   | Using Simulators                                    | 256 |

| 6.4 | Simula  | ting a VLIW Architecture                            | 257 |

|     | 6.4.1   | Interpretation                                      | 258 |

|     | 6.4.2   | Compiled Simulation                                 | 259 |

|     |         | Memory                                              | 262 |

|     |         | Registers                                           | 263 |

|     |         | Control Flow                                        | 263 |

|     |         | Exceptions                                          | 266 |

|     |         | Analysis of Compiled Simulation                 | 267 |

|-----|---------|-------------------------------------------------|-----|

|     |         | Performance Measurement and Compiled Simulation | 268 |

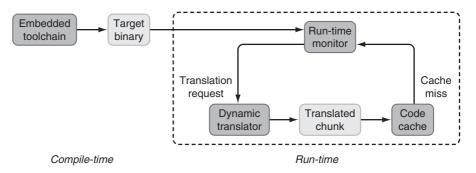

|     | 6.4.3   | Dynamic Binary Translation                      | 268 |

|     | 6.4.4   | Trace-driven Simulation                         | 270 |

| 6.5 | System  | Simulation                                      | 271 |

|     | 6.5.1   | I/O and Concurrent Activities                   | 272 |

|     | 6.5.2   | Hardware Simulation                             | 272 |

|     |         | Discrete Event Simulation                       | 274 |

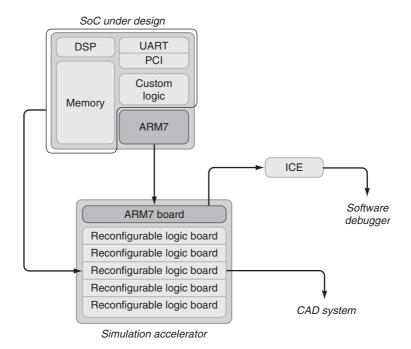

|     | 6.5.3   | Accelerating Simulation                         | 275 |

|     |         | In-Circuit Emulation                            | 275 |

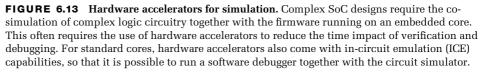

|     |         | Hardware Accelerators for Simulation            | 276 |

| 6.6 | Validat | ion and Verification                            | 276 |

|     | 6.6.1   | Co-simulation                                   | 278 |

|     | 6.6.2   | Simulation, Verification, and Test              | 279 |

|     |         | Formal Verification                             | 280 |

|     |         | Design for Testability                          | 280 |

|     |         | Debugging Support for SoC                       | 281 |

| 6.7 | Further | Reading                                         | 282 |

| 6.8 | Exercis | es                                              | 284 |

|     |         |                                                 |     |

| Emł | bedded   | Compiling and Toolchains                 | 287 |

|-----|----------|------------------------------------------|-----|

| 7.1 | What Is  | Important in an ILP Compiler?            | 287 |

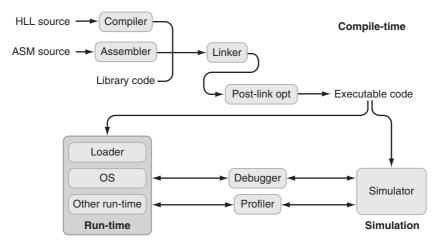

| 7.2 | Embedd   | led Cross-Development Toolchains         | 290 |

|     | 7.2.1    | Compiler                                 | 291 |

|     | 7.2.2    | Assembler                                | 292 |

|     | 7.2.3    | Libraries                                | 294 |

|     | 7.2.4    | Linker                                   | 296 |

|     | 7.2.5    | Post-link Optimizer                      | 297 |

|     | 7.2.6    | Run-time Program Loader                  | 297 |

|     | 7.2.7    | Simulator                                | 299 |

|     | 7.2.8    | Debuggers and Monitor ROMs               | 300 |

|     | 7.2.9    | Automated Test Systems                   | 301 |

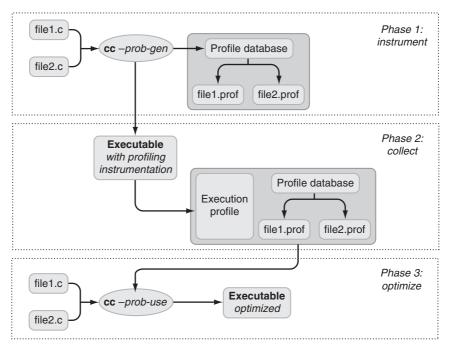

|     | 7.2.10   | Profiling Tools                          | 302 |

|     | 7.2.11   | Binary Utilities                         | 302 |

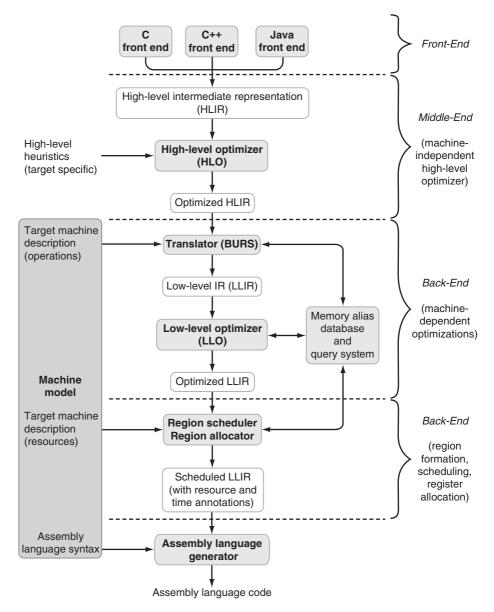

| 7.3 | Structur | re of an ILP Compiler                    | 302 |

|     | 7.3.1    | Front End                                | 304 |

|     | 7.3.2    | Machine-independent Optimizer            | 304 |

|     | 7.3.3    | Back End: Machine-specific Optimizations | 306 |

| 7.4 | Code La  | iyout                                    | 306 |

|     | 7.4.1    | Code Layout Techniques                   | 306 |

|     |          | DAG-based Placement                      | 308 |

|     |          | The "Pettis-Hansen" Technique            | 310 |

|     |          | Procedure Inlining                        | 310 |

|-----|----------|-------------------------------------------|-----|

|     |          | Cache Line Coloring                       | 311 |

|     |          | Temporal-order Placement                  | 311 |

| 7.5 | Embedd   | led-Specific Tradeoffs for Compilers      | 311 |

|     | 7.5.1    | Space, Time, and Energy Tradeoffs         | 312 |

|     | 7.5.2    | Power-specific Optimizations              | 315 |

|     |          | Fundamentals of Power Dissipation         | 316 |

|     |          | Power-aware Software Techniques           | 317 |

| 7.6 | DSP-Sp   | ecific Compiler Optimizations             | 320 |

|     | 7.6.1    | Compiler-visible Features of DSPs         | 322 |

|     |          | Heterogeneous Registers                   | 322 |

|     |          | Addressing Modes                          | 322 |

|     |          | Limited Connectivity                      | 323 |

|     |          | Local Memories                            | 323 |

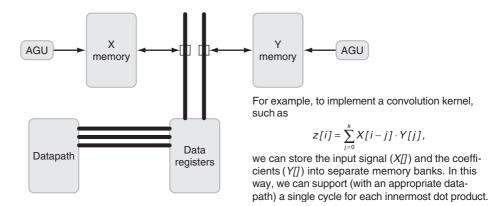

|     |          | Harvard Architecture                      | 324 |

|     | 7.6.2    | Instruction Selection and Scheduling      | 325 |

|     | 7.6.3    | Address Computation and Offset Assignment | 327 |

|     | 7.6.4    | Local Memories                            | 327 |

|     | 7.6.5    | Register Assignment Techniques            | 328 |

|     | 7.6.6    | Retargetable DSP and ASIP Compilers       | 329 |

| 7.7 | Further  | Reading                                   | 332 |

| 7.8 | Exercise | es                                        | 333 |

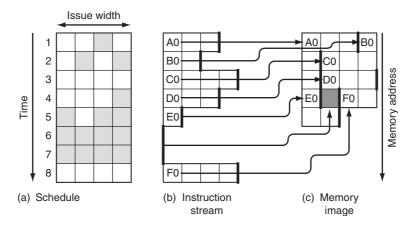

| Cor | npiling  | g for VLIWs and ILP                                 | 337 |

|-----|----------|-----------------------------------------------------|-----|

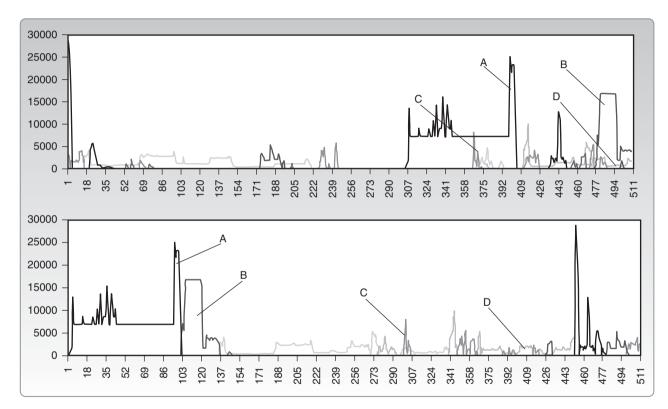

| 8.1 | Profilir | ıg                                                  | 338 |

|     | 8.1.1    | Types of Profiles                                   | 338 |

|     | 8.1.2    | Profile Collection                                  | 341 |

|     | 8.1.3    | Synthetic Profiles (Heuristics in Lieu of Profiles) | 341 |

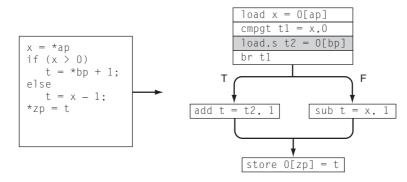

|     | 8.1.4    | Profile Bookkeeping and Methodology                 | 342 |

|     | 8.1.5    | Profiles and Embedded Applications                  | 342 |

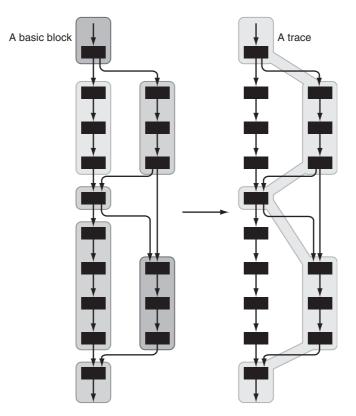

| 8.2 | Schedu   | ıling                                               | 343 |

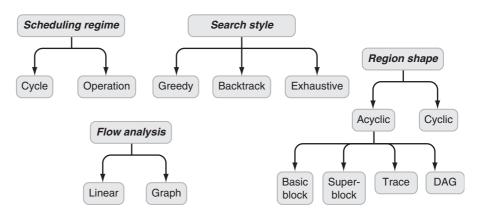

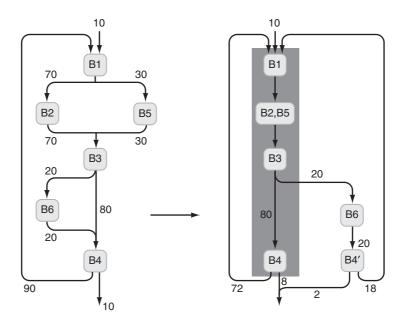

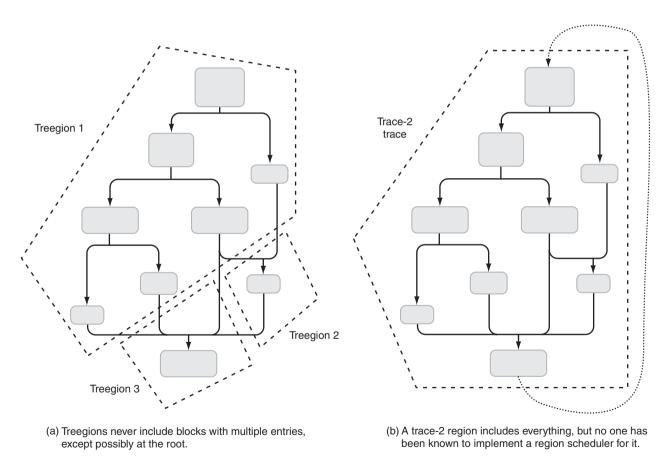

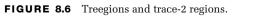

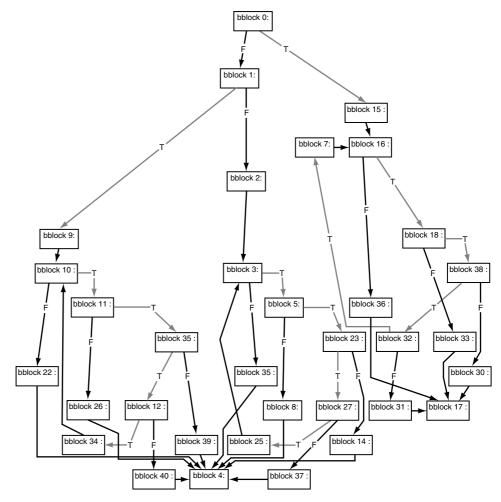

|     | 8.2.1    | Acyclic Region Types and Shapes                     | 345 |

|     |          | Basic Blocks                                        | 345 |

|     |          | Traces                                              | 345 |

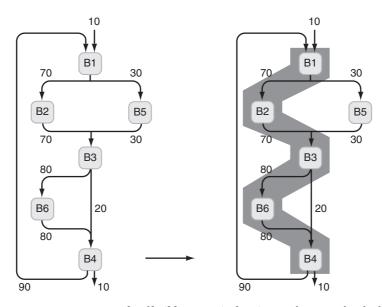

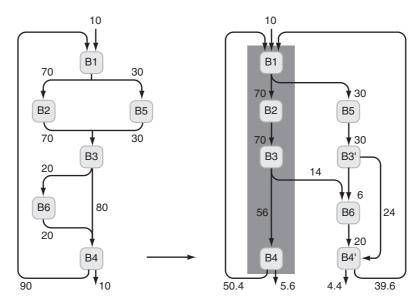

|     |          | Superblocks                                         | 345 |

|     |          | Hyperblocks                                         | 347 |

|     |          | Treegions                                           | 347 |

|     |          | Percolation Scheduling                              | 348 |

|     | 8.2.2    | Region Formation                                    | 350 |

|     |          | Region Selection                                    | 351 |

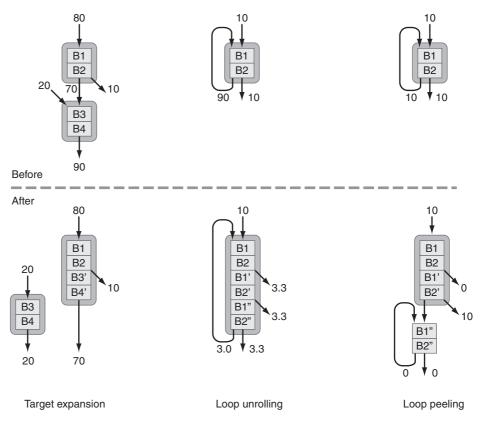

|     |          | Enlargement Techniques                              | 353 |

|     |          | Phase-ordering Considerations                       | 356 |

|     |          |                                                     |     |

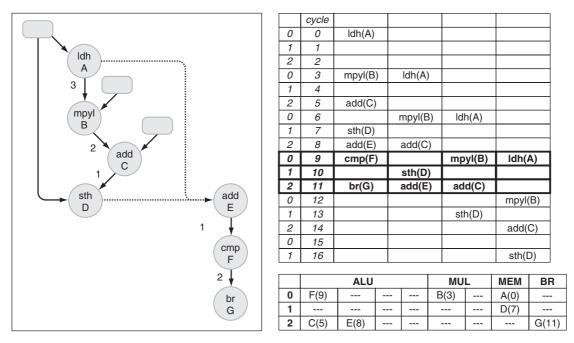

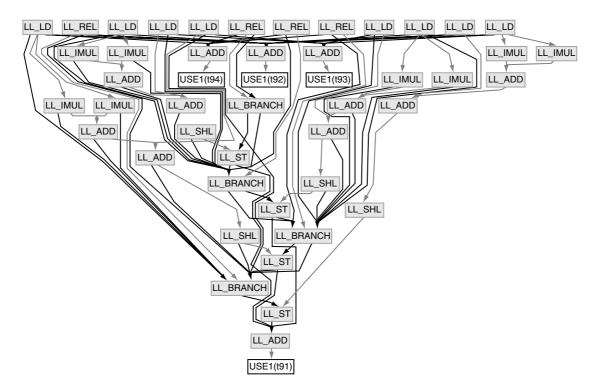

|     | 8.2.3    | Schedule Construction                        | 357 |

|-----|----------|----------------------------------------------|-----|

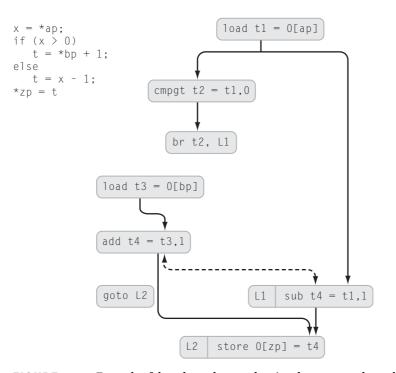

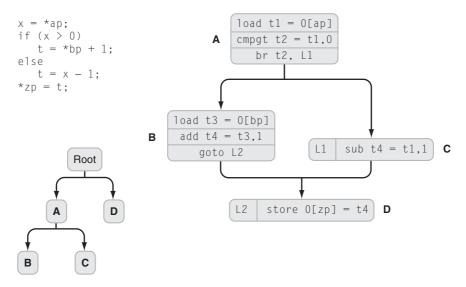

|     |          | Analyzing Programs for Schedule Construction | 359 |

|     |          | Compaction Techniques                        | 362 |

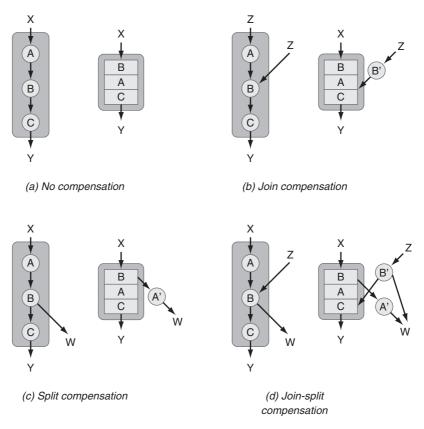

|     |          | Compensation Code                            | 365 |

|     |          | Another View of Scheduling Problems          | 367 |

|     | 8.2.4    | Resource Management During Scheduling        | 368 |

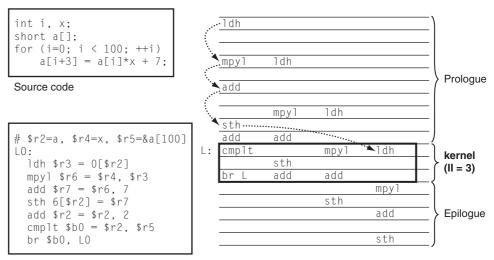

|     |          | Resource Vectors                             | 368 |

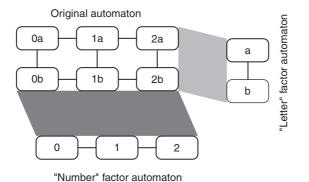

|     |          | Finite-state Automata                        | 369 |

|     | 8.2.5    | Loop Scheduling                              | 371 |

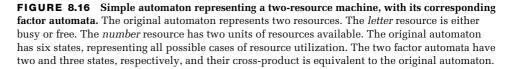

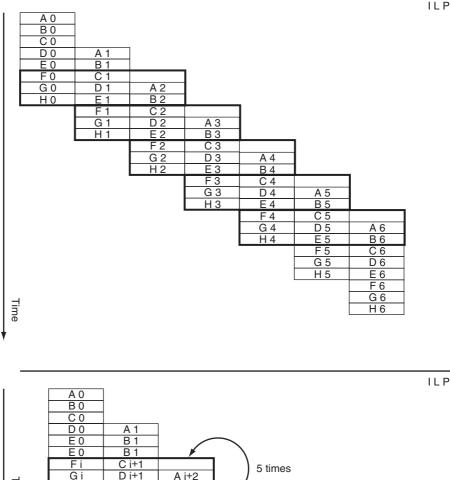

|     |          | Modulo Scheduling                            | 373 |

|     | 8.2.6    | Clustering                                   | 380 |

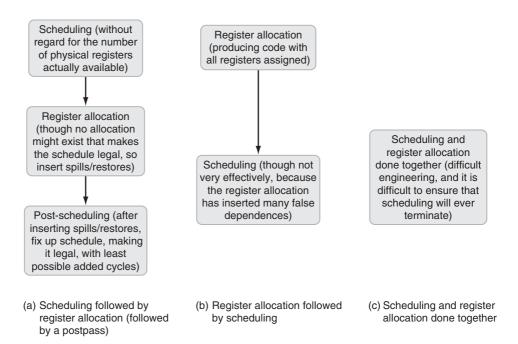

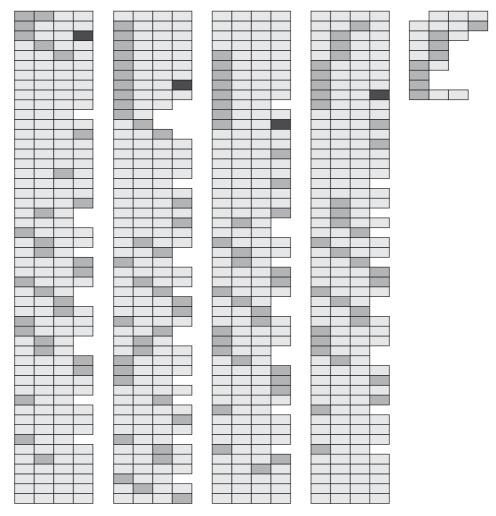

| 8.3 | Register | Allocation                                   | 382 |

|     | 8.3.1    | Phase-ordering Issues                        | 383 |

|     |          | Register Allocation and Scheduling           | 383 |

| 8.4 | Specula  | tion and Predication                         | 385 |

|     | 8.4.1    | Control and Data Speculation                 | 385 |

|     | 8.4.2    | Predicated Execution                         | 386 |

|     | 8.4.3    | Prefetching                                  | 389 |

|     | 8.4.4    | Data Layout Methods                          | 390 |

|     | 8.4.5    | Static and Hybrid Branch Prediction          | 390 |

| 8.5 | Instruct | ion Selection                                | 390 |

| 8.6 | Further  | Reading                                      | 391 |

| 8.7 | Exercise | 98                                           | 395 |

|     |          |                                              |     |

| The | Run-ti   | me System                            | 399 |

|-----|----------|--------------------------------------|-----|

| 9.1 | Exceptio | ons, Interrupts, and Traps           | 400 |

|     | 9.1.1    | Exception Handling                   | 400 |

| 9.2 | Applica  | tion Binary Interface Considerations | 402 |

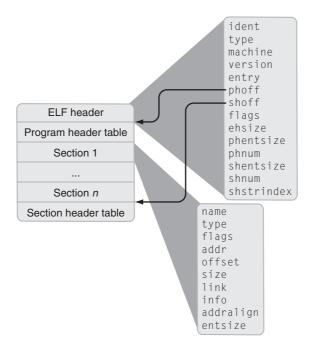

|     | 9.2.1    | Loading Programs                     | 404 |

|     | 9.2.2    | Data Layout                          | 406 |

|     | 9.2.3    | Accessing Global Data                | 407 |

|     | 9.2.4    | Calling Conventions                  | 409 |

|     |          | Registers                            | 409 |

|     |          | Call Instructions                    | 409 |

|     |          | Call Sites                           | 410 |

|     |          | Function Prologues and Epilogues     | 412 |

|     | 9.2.5    | Advanced ABI Topics                  | 412 |

|     |          | Variable-length Argument Lists       | 412 |

|     |          | Dynamic Stack Allocation             | 413 |

|     |          | Garbage Collection                   | 414 |

|     |          | Linguistic Exceptions                | 414 |

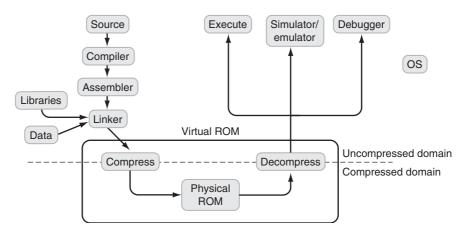

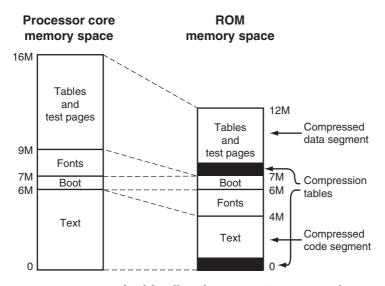

| 9.3 | Code C  | ompression                             | 415 |

|-----|---------|----------------------------------------|-----|

|     | 9.3.1   | Motivations                            | 416 |

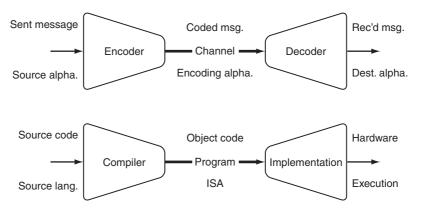

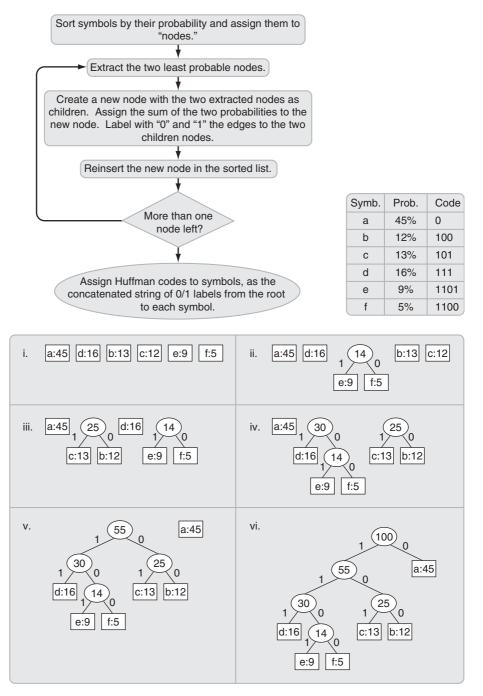

|     | 9.3.2   | Compression and Information Theory     | 417 |

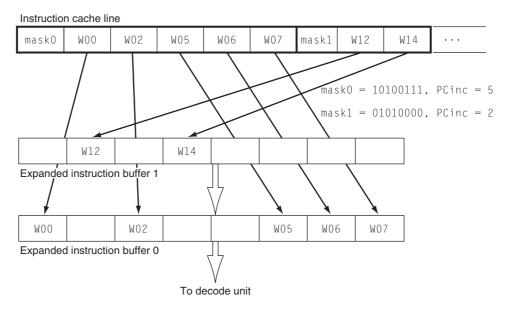

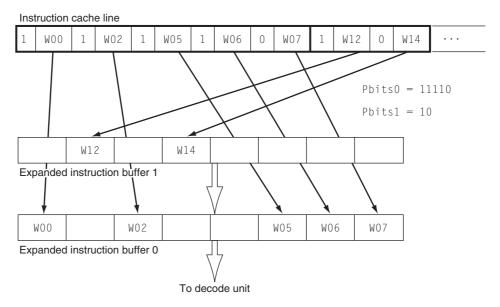

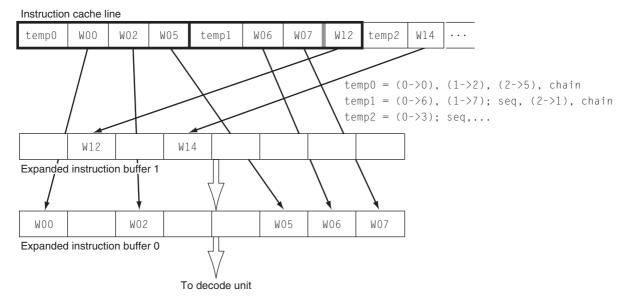

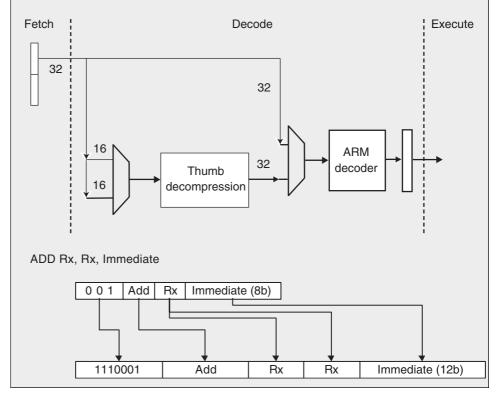

|     | 9.3.3   | Architectural Compression Options      | 417 |

|     |         | Decompression on Fetch                 | 420 |

|     |         | Decompression on Refill                | 420 |

|     |         | Load-time Decompression                | 420 |

|     | 9.3.4   | Compression Methods                    | 420 |

|     |         | Hand-tuned ISAs                        | 421 |

|     |         | Ad Hoc Compression Schemes             | 421 |

|     |         | RAM Decompression                      | 422 |

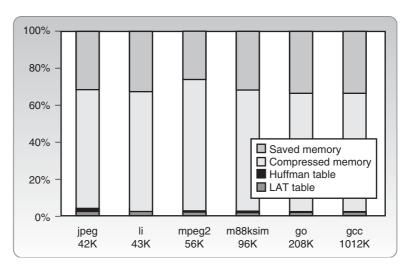

|     |         | Dictionary-based Software Compression  | 422 |

|     |         | Cache-based Compression                | 422 |

|     |         | Quantifying Compression Benefits       | 424 |

| 9.4 | Embed   | ded Operating Systems                  | 427 |

|     | 9.4.1   | "Traditional" OS Issues Revisited      | 427 |

|     | 9.4.2   | Real-time Systems                      | 428 |

|     |         | Real-time Scheduling                   | 429 |

|     | 9.4.3   | Multiple Flows of Control              | 431 |

|     |         | Threads, Processes, and Microkernels   | 432 |

|     | 9.4.4   | Market Considerations                  | 433 |

|     |         | Embedded Linux                         | 435 |

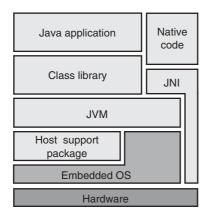

|     | 9.4.5   | Downloadable Code and Virtual Machines | 436 |

| 9.5 | Multip  | rocessing and Multithreading           | 438 |

|     | 9.5.1   | Multiprocessing in the Embedded World  | 438 |

|     | 9.5.2   | Multiprocessing and VLIW               | 439 |

| 9.6 | Further | Reading                                | 440 |

| 9.7 | Exercis | es                                     | 441 |

| Application Design and Customization |         |                                            | 443 |

|--------------------------------------|---------|--------------------------------------------|-----|

| 10.1                                 | Program | ıming Language Choices                     | 443 |

|                                      | 10.1.1  | Overview of Embedded Programming Languages | 444 |

|                                      | 10.1.2  | Traditional C and ANSI C                   | 445 |

|                                      | 10.1.3  | C++ and Embedded C++                       | 447 |

|                                      |         | Embedded C++                               | 449 |

|                                      | 10.1.4  | Matlab                                     | 450 |

|                                      | 10.1.5  | Embedded Java                              | 452 |

|                                      |         | The Allure of Embedded Java                | 452 |

|                                      |         | Embedded Java: The Dark Side               | 455 |

|                                      | 10.1.6  | C Extensions for Digital Signal Processing | 456 |

|                                      |         | Restricted Pointers                        | 456 |

|                                      |         | Fixed-point Data Types                     | 459 |

|                                      |         | Circular Arrays                            | 461 |

|          | Matrix Referencing and Operators                                                                                                   | 462                                                                                                                                                                                                            |

|----------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

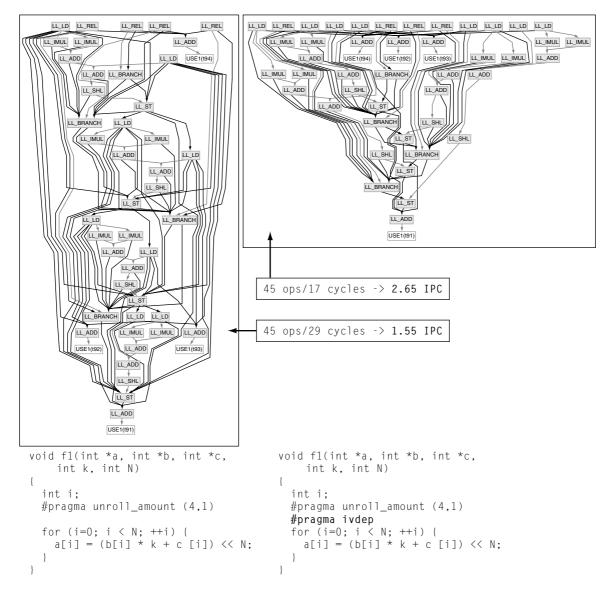

| 10.1.7   | Pragmas, Intrinsics, and Inline Assembly Language Code                                                                             | 462                                                                                                                                                                                                            |

|          | Compiler Pragmas and Type Annotations                                                                                              | 462                                                                                                                                                                                                            |

|          | Assembler Inserts and Intrinsics                                                                                                   | 463                                                                                                                                                                                                            |

| Perform  | ance, Benchmarking, and Tuning                                                                                                     | 465                                                                                                                                                                                                            |

| 10.2.1   | Importance and Methodology                                                                                                         | 465                                                                                                                                                                                                            |

| 10.2.2   | Tuning an Application for Performance                                                                                              | 466                                                                                                                                                                                                            |

|          | Profiling                                                                                                                          | 466                                                                                                                                                                                                            |

|          | Performance Tuning and Compilers                                                                                                   | 467                                                                                                                                                                                                            |

|          | Developing for ILP Targets                                                                                                         | 468                                                                                                                                                                                                            |

| 10.2.3   | Benchmarking                                                                                                                       | 473                                                                                                                                                                                                            |

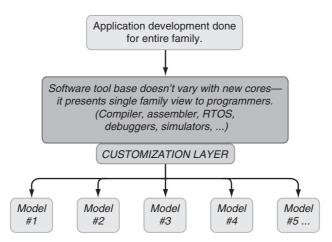

| Scalabil | lity and Customizability                                                                                                           | 475                                                                                                                                                                                                            |

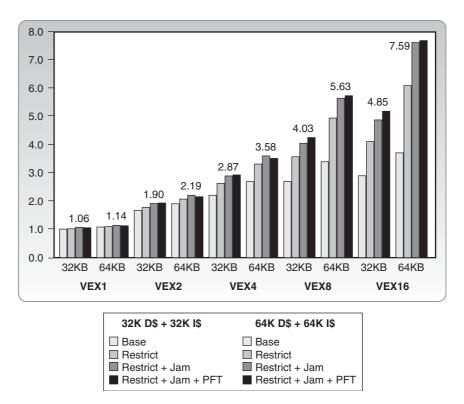

| 10.3.1   | Scalability and Architecture Families                                                                                              | 476                                                                                                                                                                                                            |

| 10.3.2   | Exploration and Scalability                                                                                                        | 477                                                                                                                                                                                                            |

| 10.3.3   | Customization                                                                                                                      | 478                                                                                                                                                                                                            |

|          | Customized Implementations                                                                                                         | 479                                                                                                                                                                                                            |

| 10.3.4   | Reconfigurable Hardware                                                                                                            | 480                                                                                                                                                                                                            |

|          | Using Programmable Logic                                                                                                           | 480                                                                                                                                                                                                            |

| 10.3.5   | Customizable Processors and Tools                                                                                                  | 481                                                                                                                                                                                                            |

|          | Describing Processors                                                                                                              | 481                                                                                                                                                                                                            |

| 10.3.6   | Tools for Customization                                                                                                            | 483                                                                                                                                                                                                            |

|          | Customizable Compilers                                                                                                             | 485                                                                                                                                                                                                            |

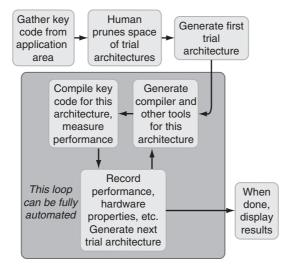

| 10.3.7   | Architecture Exploration                                                                                                           | 487                                                                                                                                                                                                            |

|          | Dealing with the Complexity                                                                                                        | 488                                                                                                                                                                                                            |

|          | Other Barriers to Customization                                                                                                    | 488                                                                                                                                                                                                            |

|          | Wrapping Up                                                                                                                        | 489                                                                                                                                                                                                            |

| Further  | Reading                                                                                                                            | 489                                                                                                                                                                                                            |

| Exercise | 98                                                                                                                                 | 490                                                                                                                                                                                                            |

|          | Perform<br>10.2.1<br>10.2.2<br>10.2.3<br>Scalabil<br>10.3.1<br>10.3.2<br>10.3.3<br>10.3.4<br>10.3.5<br>10.3.6<br>10.3.7<br>Further | <ul> <li>10.1.7 Pragmas, Intrinsics, and Inline Assembly Language Code<br/>Compiler Pragmas and Type Annotations<br/>Assembler Inserts and Intrinsics</li> <li>Performance, Benchmarking, and Tuning</li></ul> |

| App  | Application Areas |                                |     |

|------|-------------------|--------------------------------|-----|

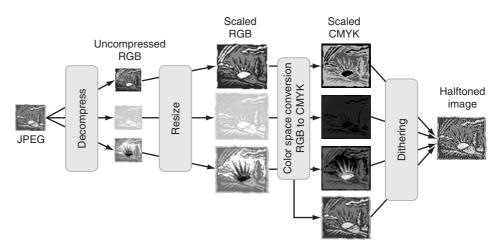

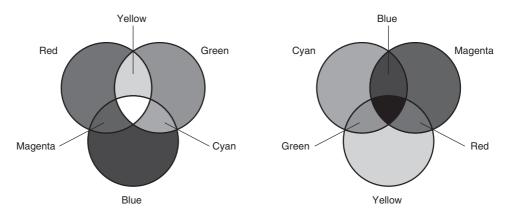

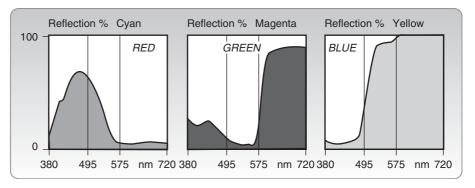

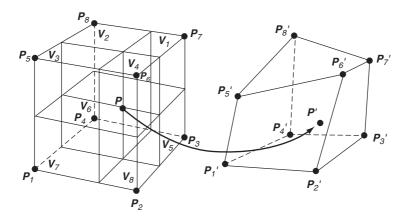

| 11.1 | Digital F         | Printing and Imaging           | 493 |

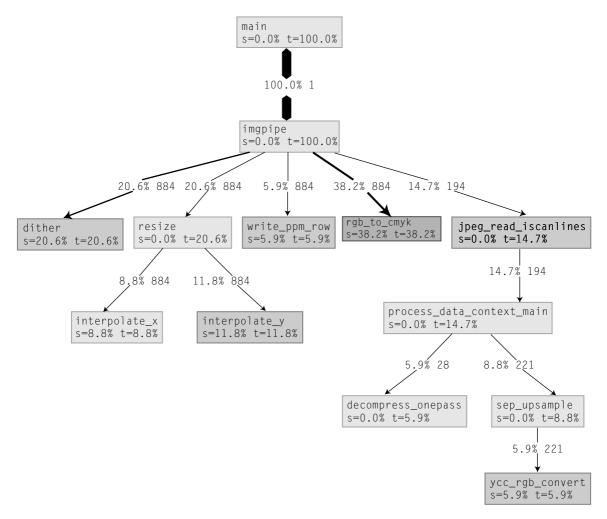

|      | 11.1.1            | Photo Printing Pipeline        | 495 |

|      |                   | JPEG Decompression             | 495 |

|      |                   | Scaling                        | 496 |

|      |                   | Color Space Conversion         | 497 |

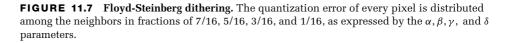

|      |                   | Dithering                      | 499 |

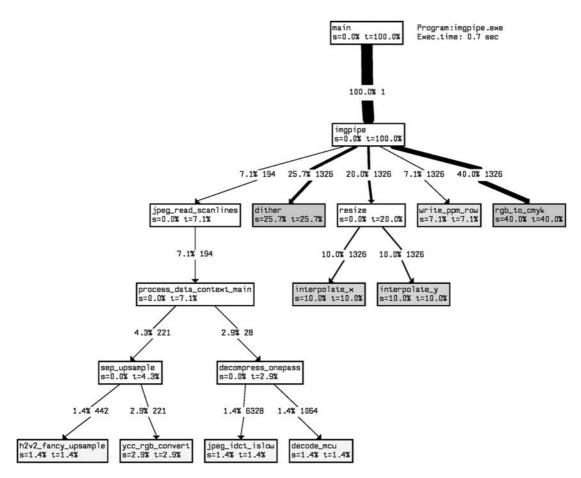

|      | 11.1.2            | Implementation and Performance | 501 |

|      |                   | Summary                        | 505 |

| 11.2 | Telecom           | 1 Applications                 | 505 |

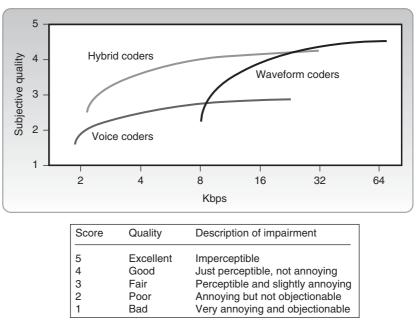

|      | 11.2.1            | Voice Coding                   | 506 |

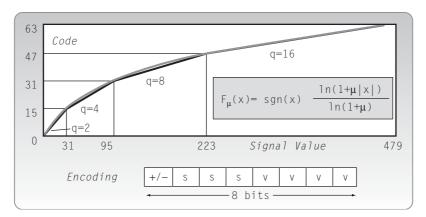

|      |                   | Waveform Codecs                | 506 |

|      |                   | Vocoders                       | 507 |

|      |                   | Hybrid Coders                  | 508 |

|      | 11.2.2   | Multiplexing                                  | 509 |

|------|----------|-----------------------------------------------|-----|

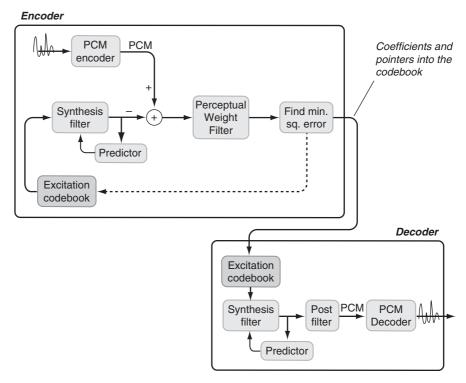

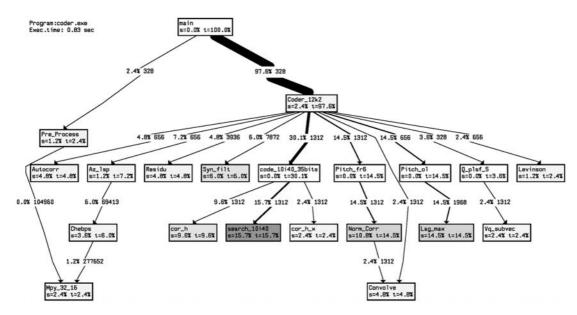

|      | 11.2.3   | The GSM Enhanced Full-rate Codec              | 510 |

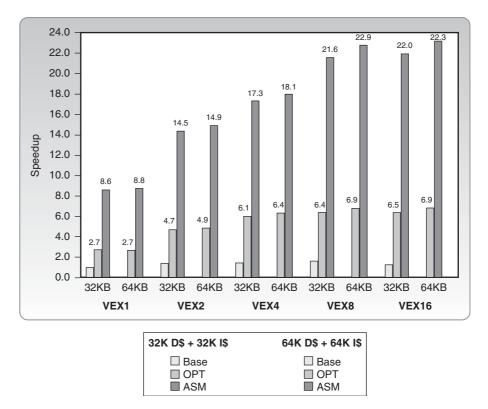

|      |          | Implementation and Performance                | 510 |

| 11.3 | Other A  | pplication Areas                              | 514 |

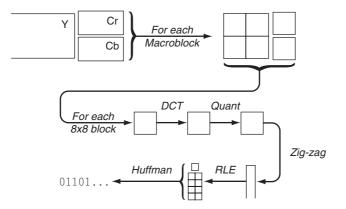

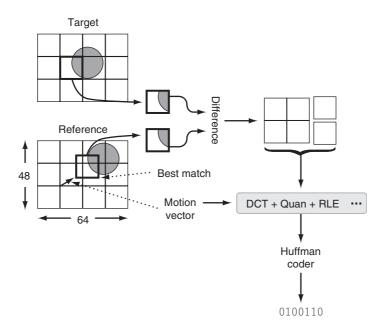

|      | 11.3.1   | Digital Video                                 | 515 |

|      |          | MPEG-1 and MPEG-2                             | 516 |

|      |          | MPEG-4                                        | 518 |

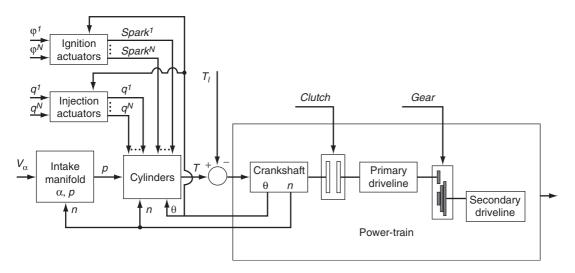

|      | 11.3.2   | Automotive                                    | 518 |

|      |          | Fail-safety and Fault Tolerance               | 519 |

|      |          | Engine Control Units                          | 520 |

|      |          | In-vehicle Networking                         | 520 |

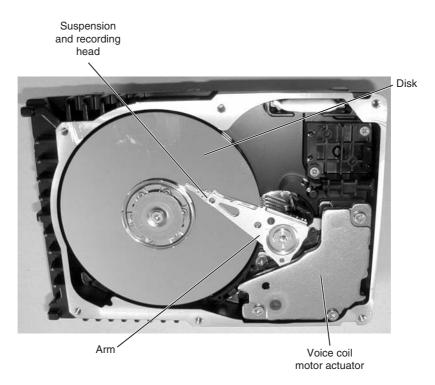

|      | 11.3.3   | Hard Disk Drives                              | 522 |

|      |          | Motor Control                                 | 524 |

|      |          | Data Decoding                                 | 525 |

|      |          | Disk Scheduling and On-disk Management Tasks  | 526 |

|      |          | Disk Scheduling and Off-disk Management Tasks | 527 |

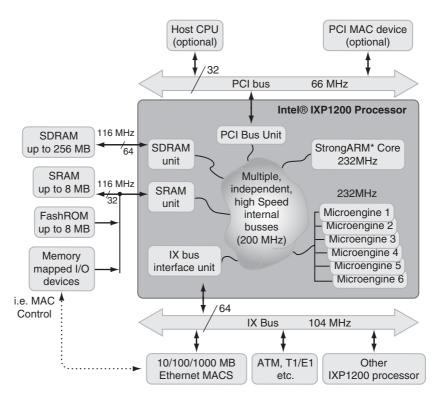

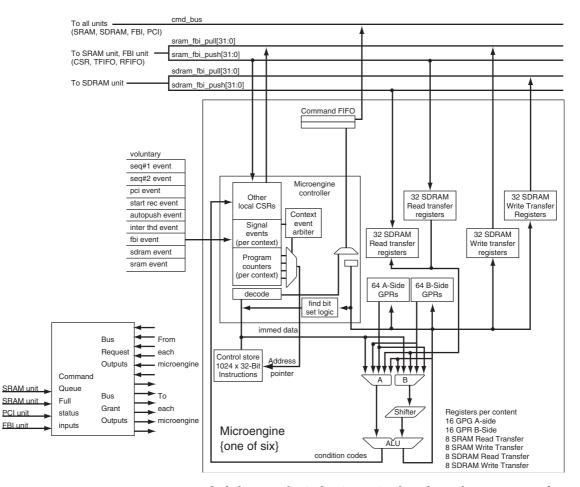

|      | 11.3.4   | Networking and Network Processors             | 528 |

|      |          | Network Processors                            | 531 |

| 11.4 | Further  | Reading                                       | 535 |

| 11.5 | Exercise | 98                                            | 537 |

|      |          |                                               |     |

#### APPENDIX A

| The | VEX S  | System                               | 539 |

|-----|--------|--------------------------------------|-----|

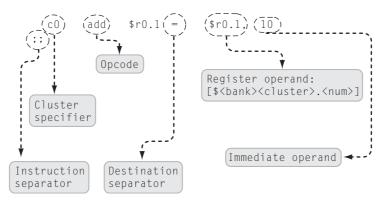

| A.1 | The VE | X Instruction-set Architecture       | 540 |

|     | A.1.1  | VEX Assembly Language Notation       | 541 |

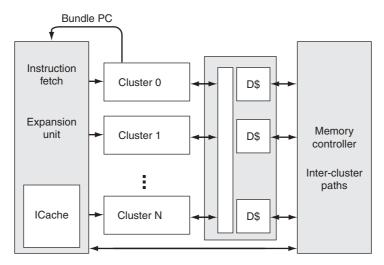

|     | A.1.2  | Clusters                             | 542 |

|     | A.1.3  | Execution Model                      | 544 |

|     | A.1.4  | Architecture State                   | 545 |

|     | A.1.5  | Arithmetic and Logic Operations      | 545 |

|     |        | Examples                             | 547 |

|     | A.1.6  | Intercluster Communication           | 549 |

|     | A.1.7  | Memory Operations                    | 550 |

|     | A.1.8  | Control Operations                   | 552 |

|     |        | Examples                             | 553 |

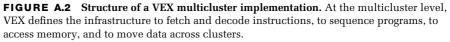

|     | A.1.9  | Structure of the Default VEX Cluster | 554 |

|     |        | Register Files and Immediates        | 555 |

|     | A.1.10 | VEX Semantics                        | 556 |

| A.2 | The VE | X Run-time Architecture              | 558 |

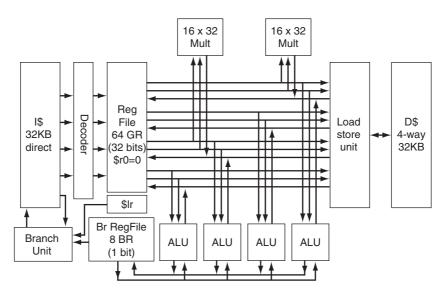

|     | A.2.1  | Data Allocation and Layout           | 559 |

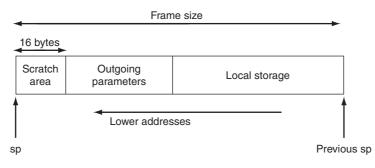

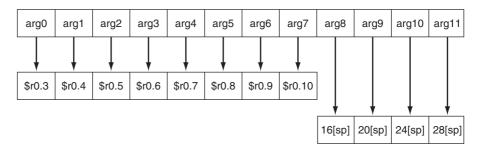

|     | A.2.2  | Register Usage                       | 560 |

|     | A.2.3  | Stack Layout and Procedure Linkage   | 560 |

|     |        | Procedure Linkage                    | 563 |

| <b>A.3</b>   | The VEX C Compiler |                                     | 566 |

|--------------|--------------------|-------------------------------------|-----|

|              | A.3.1              | Command Line Options                | 568 |

|              |                    | Output Files                        | 569 |

|              |                    | Preprocessing                       | 570 |

|              |                    | Optimization                        | 570 |

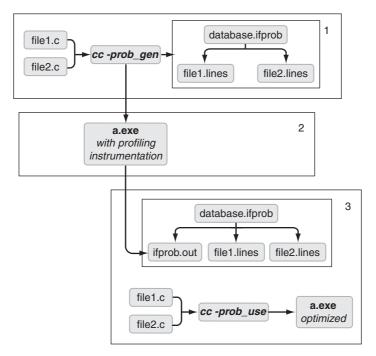

|              |                    | Profiling                           | 572 |

|              |                    | Language Definition                 | 573 |

|              |                    | Libraries                           | 574 |

|              |                    | Passing Options to Compile Phases   | 574 |

|              |                    | Terminal Output and Process Control | 575 |

|              |                    | Other Options                       | 575 |

|              | A.3.2              | Compiler Pragmas                    | 576 |

|              |                    | Unrolling and Profiling             | 576 |

|              |                    | Assertions                          | 578 |

|              |                    | Memory Disambiguation               | 578 |

|              |                    | Cache Control                       | 581 |

|              | A.3.3              | Inline Expansion                    | 583 |

|              |                    | Multiflow-style Inlining            | 583 |

|              |                    | C99-style Inlining                  | 584 |

|              | A.3.4              | Machine Model Parameters            | 585 |

|              | A.3.5              | Custom Instructions                 | 586 |

| <b>A.4</b>   | Visuali            | Visualization Tools                 |     |

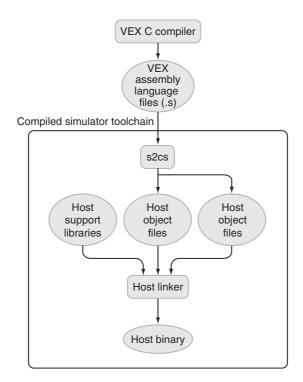

| A.5          |                    |                                     | 589 |

|              | A.5.1              | gprof Support                       | 591 |

|              | A.5.2              | Simulating Custom Instructions      | 594 |

|              | A.5.3              | Simulating the Memory Hierarchy     | 595 |

|              |                    | nizing the VEX Toolchain            | 596 |

|              | A.6.1              | Clusters                            | 596 |

|              | A.6.2              | Machine Model Resources             | 597 |

|              | A.6.3              | Memory Hierarchy Parameters         | 599 |

| A.7          | Exampl             | les of Tool Usage                   | 599 |

|              | A.7.1              | Compile and Run                     | 599 |

|              | A.7.2              | Profiling                           | 602 |

|              | A.7.3              | Custom Architectures                | 603 |

| A.8          |                    | es                                  | 605 |

|              |                    |                                     |     |

| APPENDIX B   |                    |                                     |     |

| Glossary     |                    |                                     | 607 |

| GIU          | 55a1 y             |                                     | 607 |

| APPENDIX C   |                    |                                     |     |

|              |                    |                                     |     |

| Bibliography |                    |                                     | 631 |

| Index        |                    |                                     | 661 |

TEAM LING – LIVE, INformative, Non-cost and Genuine !

# Preface

Where the end of the e

Since this is a book about embedded computing, we define and explore that world in general, but with the strongest emphasis on the processing aspects. Then, within this new world of embedded, we show how the VLIW design philosophy matches the goals and constraints well. We hope we have done this in a way that clearly and systematically explains the unique problems in the embedded domain, while remaining approachable to those with a general background in architecture and compilation. Conversely, we also need to explain the VLIW approach and its implications and to point out the ways in which VLIW, as contrasted with other high-performance architectural techniques, is uniquely suited to the embedded world.

We think this book fills a hole in the current literature. A number of current and upcoming books cover embedded computing, but few of them take the combined hardware—software systems approach we do. While the embedded computing and digital signal processing (DSP) worlds seem exotic to those with general-purpose backgrounds, they remain *computing*. Much is common between general-purpose and embedded techniques, and after showing what is common between them, we can focus on the differences. In addition, there is no standard reference on the VLIW approach. Such a book has been needed for at least a decade, and we believe that a book explaining the VLIW design philosophy has value today. This book should be useful to engineers and designers in industry, as well as suitable as a textbook for courses that aim at seniors or first-year graduate students.

While considering the mission of our book, we came up with three different possible books on the spectrum from VLIW to embedded. The first is the previously mentioned book, purely about VLIW. The second is a book about high-performance approaches to the embedded domain, with equal emphasis on VLIW, Superscalar, digital signal processor (DSP), micro-SIMD (Single Instruction Multiple Data), and vector techniques. Our book (the third option) strikes a balance: it focuses on the VLIW approach to the embedded domain. This means we give lighter treatment to the alternative approaches but spend additional effort on drawing the connections between VLIW and embedded. However, large parts of the information in our book overlap material that would go into the other two, and we think of this book as valuable for those with a strong interest in embedded computing but only a little interest in VLIW, and vice versa.

Along the way, we have tried to present our particularly idiosyncratic views of embedded, VLIW, and other high-performance architectural techniques. Most of the time, we hope we have impartially presented facts. However, these topics would be terribly dry and boring if we removed all controversy. VLIW has become a significant force in embedded processing and, as we make clear, there are technical and marketing reasons for this trend to continue. We will wear our biases on our sleeves (if you can't tell from the title, we think VLIW is the correct hammer for the embedded nail), but we hope to be honest about these biases in areas that remain unresolved.

## Content and Structure

When we first wrote the outline for this book, the chapters fell into three major categories: *hardware, software,* and *applications.* Thus, the outline of the book correspondingly had three major parts. As we have written and rewritten, the organization has changed, pieces have migrated from one chapter to another, and the clean three-part organization has broken down into a set of chapters that only roughly matches the original tripartite structure. The unfortunate truth of modern computer architecture is that one cannot consider any of hardware, software, or applications by themselves.

This book really has two introductory chapters. Chapter 1 describes the world of embedded processing. It defines embedded processing, provides examples of the various types of embedded processors, describes application domains in which embedded cores are deployed, draws distinctions between the embedded and general-purpose domains, and talks about the marketplace for embedded devices. The second introductory chapter, Chapter 2, defines *instruction-level parallelism* (ILP), the primary technique for extracting performance in many modern architectural styles, and describes how compilation is crucial to any ILP-oriented processor design. Chapter 2 also describes the notion of an architectural style or design philosophy, of which VLIW is one example. Last, Chapter 2 describes how technology has evolved so that VLIW and embedded, once vastly separate domains, are now quite suited to each other.

Chapters 3 through 5 constitute the purely "hardware"-related part of the book. Chapter 3 describes what we mean when we say architecture or instruction-set architecture (ISA), defines what a VLIW ISA looks like, and describes in particular how VLIW architectures have been built for embedded applications. Chapter 3 also describes instruction set *encoding* at two levels. From a high-level perspective, Chapter 3 revisits the notion of design philosophy and architectural style with respect to how that style affects the way operations and instructions are encoded under each design philosophy. At a detailed level, Chapter 3 describes the particular issues associated with VLIW operation and instruction encoding.

Chapter 4 might be seen as a continuation of the previous chapter, but instead of describing ISA design as a whole (with a view across various ISA styles), Chapter 4 examines the hardware structures (such as the datapath, memory, register files, and control units) necessary to all modern processors. Chapter 4 pays particular attention to how these structures differ in the embedded domain from their general-purpose counterparts.

The next chapter explores microarchitecture, the implementation of techniques within a given ISA. Chapter 5 can be seen as largely paralleling Chapter 4 in subject matter, but it considers how to *implement* each piece of functionality rather than how to *specify* that work be done within an ISA. Chapter 5 is informed by the technological constraints of modern design; that is, wires are expensive, whereas transitors are cheap. The chapter also (very briefly) considers power-related technological concerns.

Chapter 6 fits poorly into either the hardware and software categories, as both topics occur in each of its sections. Chapter 6 begins with a description of how a system-on-achip (SoC) is designed. Most modern embedded systems today are designed using the SoC methodology. Chapter 6 continues with how processor cores integrate with SoCs. Then it describes simulation methodologies for processor cores, followed by simulation techniques for entire systems. Last, Chapter 6 describes validation and verification of simulators and their systems. It might be best to view Chapter 6 as a bridge between the hardware and software areas, or perhaps its integration of the two serves as a good illustration of the complexities involved in building hardware/software systems.

The next three chapters emphasize the software area, although reading them will make it clear that they are infused with hardware-related topics in a number of ways. Chapter 7 describes the entire *toolchain*: the suite of software programs used to analyze, design, and build the software of an embedded system. Chapter 7 also describes a number of embedded- and DSP-specific code transformations.

Chapter 8 describes a subset of the compiler optimizations and transformations in an industrial-strength ILP-oriented compiler. This book is not a compiler textbook. Our goal in this chapter is to paint a balanced picture of the suite of optimizations — including their uses, complexities, and interactions — so that system designers will understand the nature of compilation-related issues, and so that compiler designers will know where else to look.

Chapter 9 covers a broad range of topics that often fall between the cracks of traditional topics, but are nonetheless important to building a working system. Chapter 9 details issues about exceptions, application binary interfaces (ABIs), code compression, operating systems (including embedded and real-time variants), and multiprocessing. Many of these topics have a strong software component to them, but each also interacts strongly with hardware structures that support the software functionality.

The last two chapters focus on applications. Chapter 10 begins by discussing programming languages for embedded applications, and then moves on to performance, benchmarks, and tuning. Then it continues to scalability and customizability in embedded architectures, and finishes with detail about customizable processors. Chapter 11 visits a number of embedded applications at a variety of levels of detail. We spend the most time on digital printing and imaging, and telecommunications, and less time on other areas, such as automotive, network processing, and disk drives.

While writing this book, it became clear that there are a large number of terms with overlapping and conflicting meanings in this field. For example, *instruction* can mean operation, bundle, parallel issue group, or parallel execution group to different subcommunities. Wherever possible, we use the terms as they are used in the architecture field's dominant textbook, John Hennessy and Dave Patterson's *Computer Architecture:* A Quantitative Approach. The Glossary lists alternate definitions and synonyms, and indicates which terms we intend to use consistently.

## The VEX (VLIW Example) Computing System

Lest we be accused of writing an armchair textbook (like those scientists of the nineteenth century who deduced everything from first principles), our book ships with an embedded-oriented VLIW development system. We call this system VEX, for "VLIW Example." We hope it is even more useful to our readers than its textbook ancestors, MIX and DLX, were for their readers. VEX is based on production tools used at HP Labs and other laboratories. It is a piece of real-world VLIW processor technology, albeit simplified for instructional use.

VEX is intended for experimental use. It includes a number of simulators, and its tools allow hardware reconfiguration and both manual and automated design-space exploration. Code, documentation, and samples can be downloaded from the book's Web site at *http://www.vliw.org/book*. VEX examples and exercises occur throughout the book. The Appendix describes the VEX instruction set architecture and tool chain.

### Audience

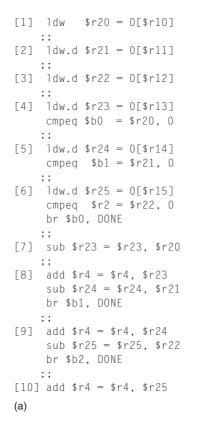

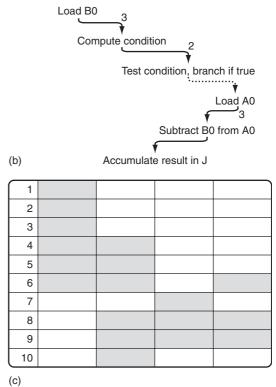

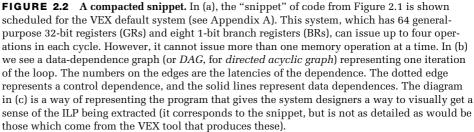

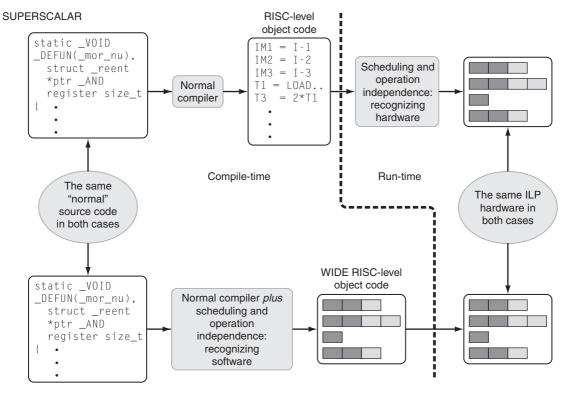

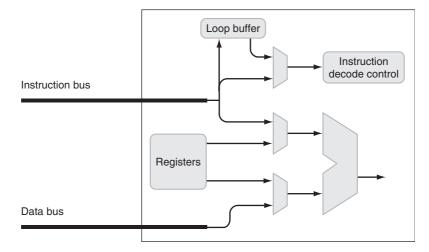

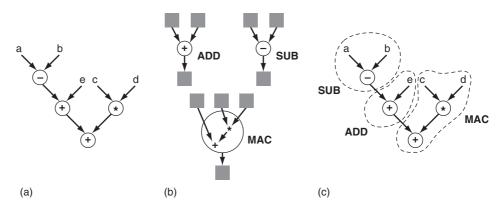

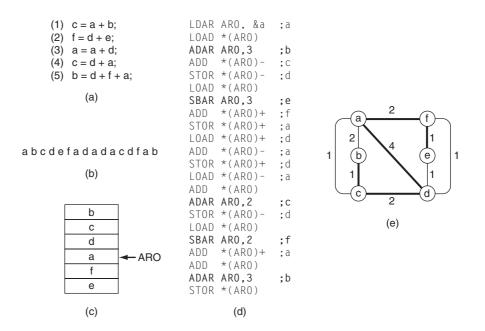

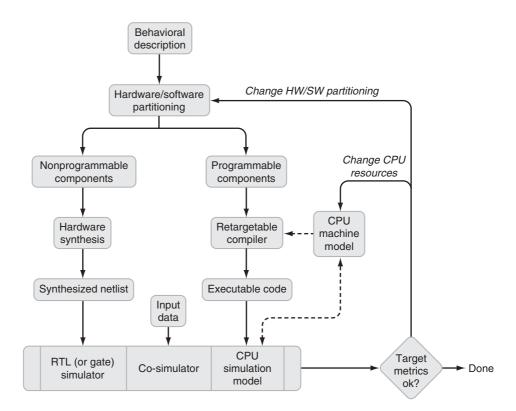

We assume a basic knowledge of computer architecture concepts, as might be given by some industrial experience or a first undergraduate course in architecture. This implies that you know the basic techniques of pipelining and caching, and that the idea of an instruction set is familiar. It helps but is not a requirement that you have some background in compilation, or at least that you believe an optimizing compiler might be useful in producing fast code for modern machines. For reasons of space, we touch on those fundamentals related to this text and for more basic information refer you to more basic architecture and compilation textbooks. Patterson and Hennessy's undergraduate architecture textbook, *Computer Organization and Design*, and Appel's polymorphic set of undergraduate compiler books, *Modern Compiler Implementation in C, Java*, and *ML* are fine places to start.