16FFC

# **FULLY DIGITAL GLITCH FREE PLL**

## **KEY FEATURES**

- Ideal as a clock generator for digital design

- Excellent frequency jitter performance

- Ultra-low area fully digital PLL design

- Patented glitch free frequency adjustment

- Fine frequency precision with fractional divider

- Low implementation charges due to predictable digital design

### **DESCRIPTION**

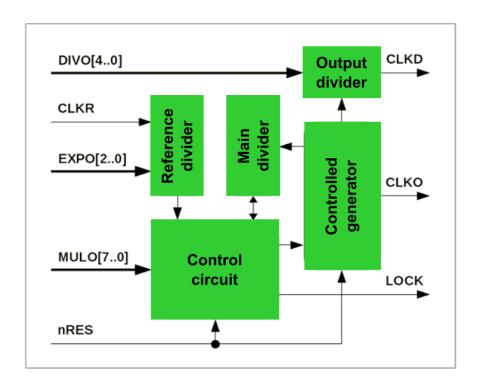

A programmable fully digital PLL (FDPLL) designed to lock to an incoming clock source and produce an output clock. It is ideal as a clock generator for digital designs, but not intended for analog blocks like ADC/DAC or SERDES clocking. This digital PLL has ultra-low area and low implementation charges due to predictable digital design.

maltsystem.com/en/product/ip-blocks

In the capture mode PLL provides periodic signal on  $\mathit{CLKO}$  output with period equal to  $\mathit{CLKR}$  inputs period multiplied by  $\mathit{MULO:EXPO}$  value. Where  $\mathit{MULO:EXPO}$  is a denormalized floating-point number,  $\mathit{MULO}$  is an  $\mathit{8}$ -bit mantissa,  $\mathit{EXPO}$  is a  $\mathit{3}$ -bit exponent. Multiplication coefficient is calculated as follows: the  $\mathit{EXPO}$  exponent code [2..0] is interpreted as integer from  $\mathit{0}$  to  $\mathit{7}$ , which determines the position of the binary point inside the  $\mathit{MULO}$  mantissa [7..0].  $\mathit{EXPO}$  numerical value is the number of the  $\mathit{MULO}$  digit, followed by a binary dot dividing  $\mathit{MULO}$  into integer and fractional parts (the size of the fractional part). That is, for  $\mathit{EXPO} = \mathit{0}$ , the fractional part is absent, and the entire integer part is in  $\mathit{MULO}$  [7..0]. For  $\mathit{EXPO} = \mathit{7}$ , the integer part is in  $\mathit{MULO}$  [7], fractional in  $\mathit{MULO}$  [6..0]. In addition to the main output of the generator, the module has an auxiliary output  $\mathit{CLKD}$ , the frequency of which is obtained by dividing the main frequency by a factor of  $\mathit{2*DIVO}$  [4..0].

### PLL CHARACTERISTICS

| Parameter                   | Unit            | Min  | Тур   | Max  | Comment       |

|-----------------------------|-----------------|------|-------|------|---------------|

| CLKR reference frequency    | MHz             | 1.2  |       | 3000 |               |

| CLKO output frequency range | MHz             | 300  |       | 3000 |               |

| CLKD output frequency       | MHz             |      |       | 1500 |               |

| CLKO jitter                 | %               |      | <2    |      | CLKO=1000 MHz |

| CLKO output duty cycle      | %               | 45   | 50    | 55   |               |

| Power consumption           | mW              |      |       | 5    |               |

| Operational voltage         | V               | 0.72 | 0.8   | 0.99 |               |

| Total area                  | mm <sup>2</sup> |      | 0.036 |      |               |

| Operational temperature     | °C              | -40  | 85    | 125  |               |

#### **PIN LIST**

| Signal   | Direction | Comment                               |  |  |

|----------|-----------|---------------------------------------|--|--|

| nRES     | input     | Asynchronous reset input (Active Low) |  |  |

| CLKR     | input     | Reference frequency input             |  |  |

| MULO[70] | input     | Multiplication factor mantissa input  |  |  |

| EXPO[20] | input     | Multiplication factor exponent input  |  |  |

| DIVO[40] | input     | Post-divider factor input             |  |  |

| CLKO     | output    | Basic frequency output                |  |  |

| CLKD     | output    | Post-divider output                   |  |  |

| LOCK     | output    | Capture indication output             |  |  |