Architecture

How does it work?

Single-type computing elements produced ‘from scratch’ for a specific class of tasks are approximately 80% of any chip we develop. These elements determine productivity and chip power engineering. There are hundreds to several thousands elements on the chip! All the computing elements are programmed in C language or in its subset. The elements are combined into groups controlled by compact universal RISC processors grouped into computational array that to a programmer looks like a typical multi-threaded processor programmed in C/C++. he classic problems of multithreaded processing (conflict resolution mechanism of simultaneous access to shared data including atomic operations) are solved in hardware at the memory controller level.

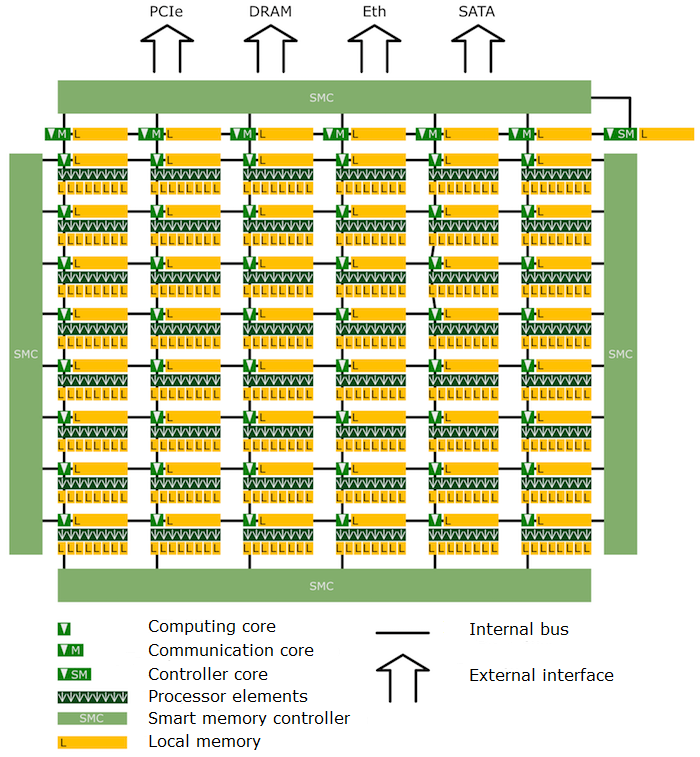

The Brief Look at MALT architecture

The basis of MALT architecture is formed by dozens to hundreds (depends on a model) compact asynchronous universal computing cores grouped by single or several original worm-hole networks with fat-tree topology. The communication between the networks is software and hardware. The universal core hierarchy consists of 3 levels: supermaster (controller core), master (communication cores), slave (computing cores available for user’s tasks. Slave cores may contain vector accelerators (depends on a model) performing specialized tasks of a target class. Every accelerator has 8 to 128 one-type computing elements with shared instruction memory. All computing cores and accelerators have own local data memory. All universal cores directly address DRAM and other shared resources (PCIe, Ethernet, SATA). The access arbitration to external resources is provided by smart memory controller (SMC) - a ‘smart memory’ hardware controller with an additional flag of data availability. The amount of SMC, the list and the configuration of shared external resources depend on MALT Family and are defined by requirements of the target tasks.