The processor for network traffic applications has been sent to the factory

- Details

- Published: Friday, 30 July 2021 10:00

|

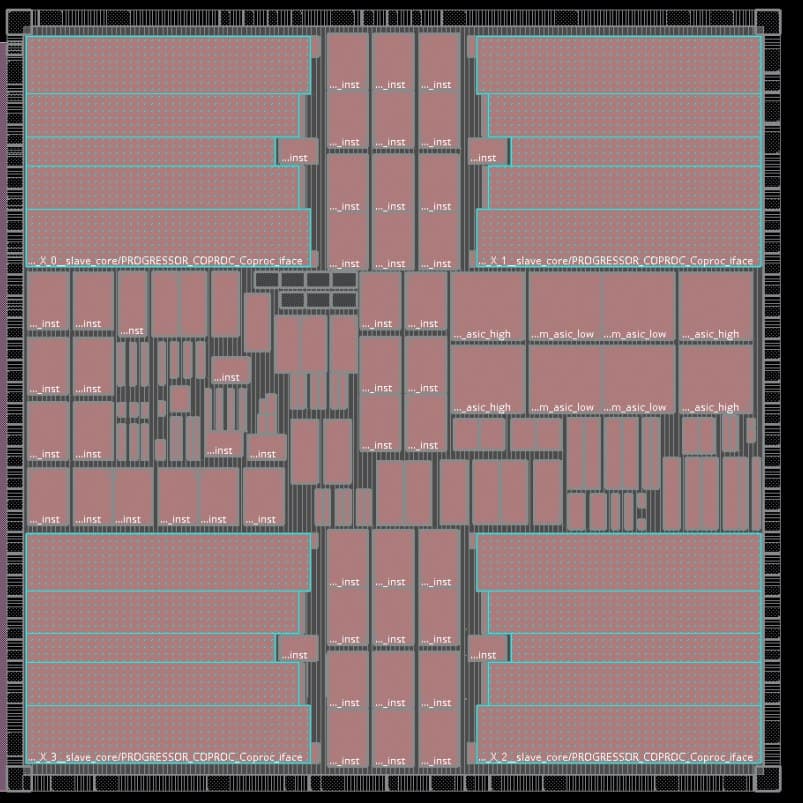

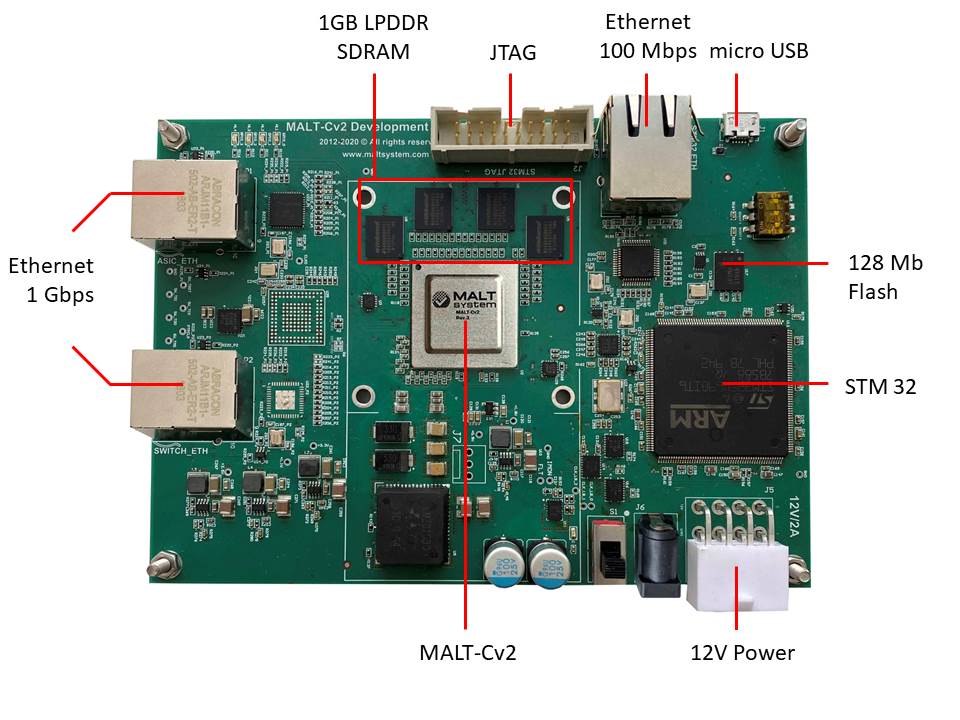

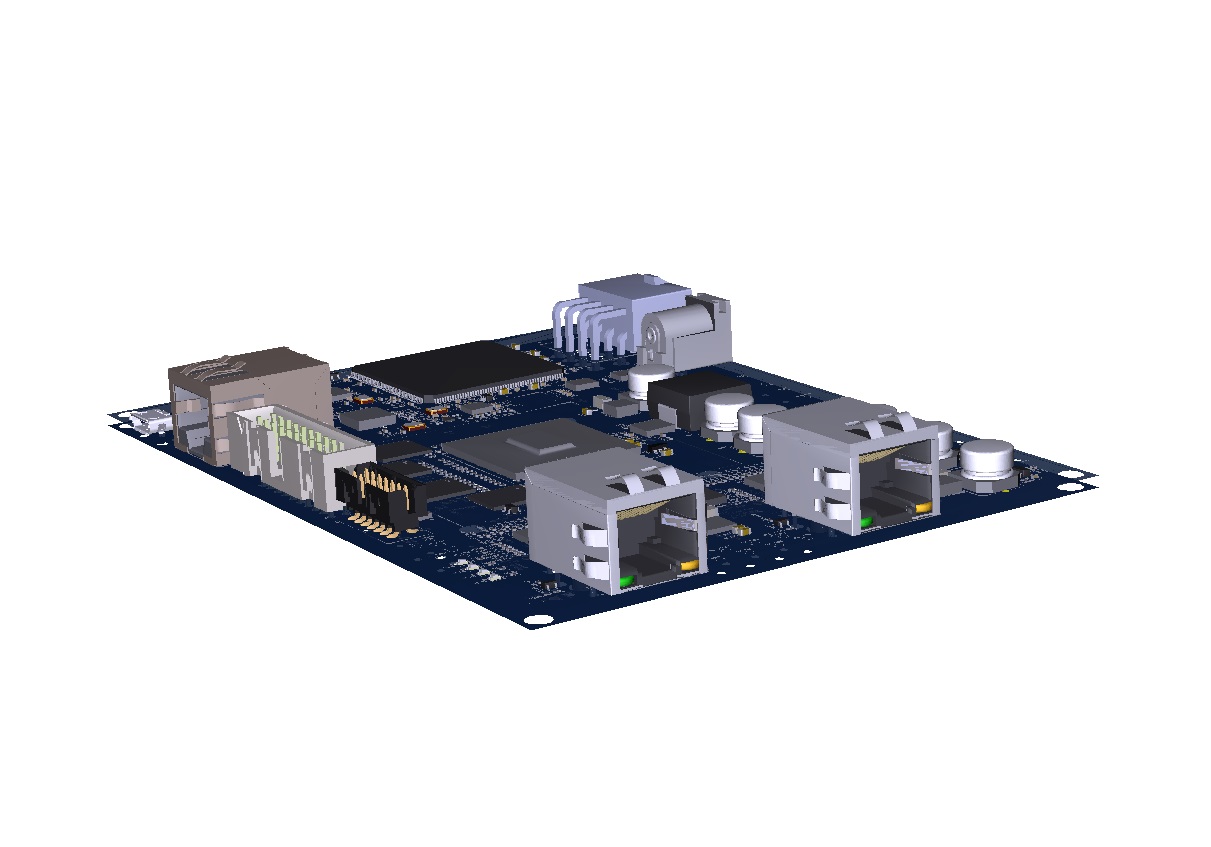

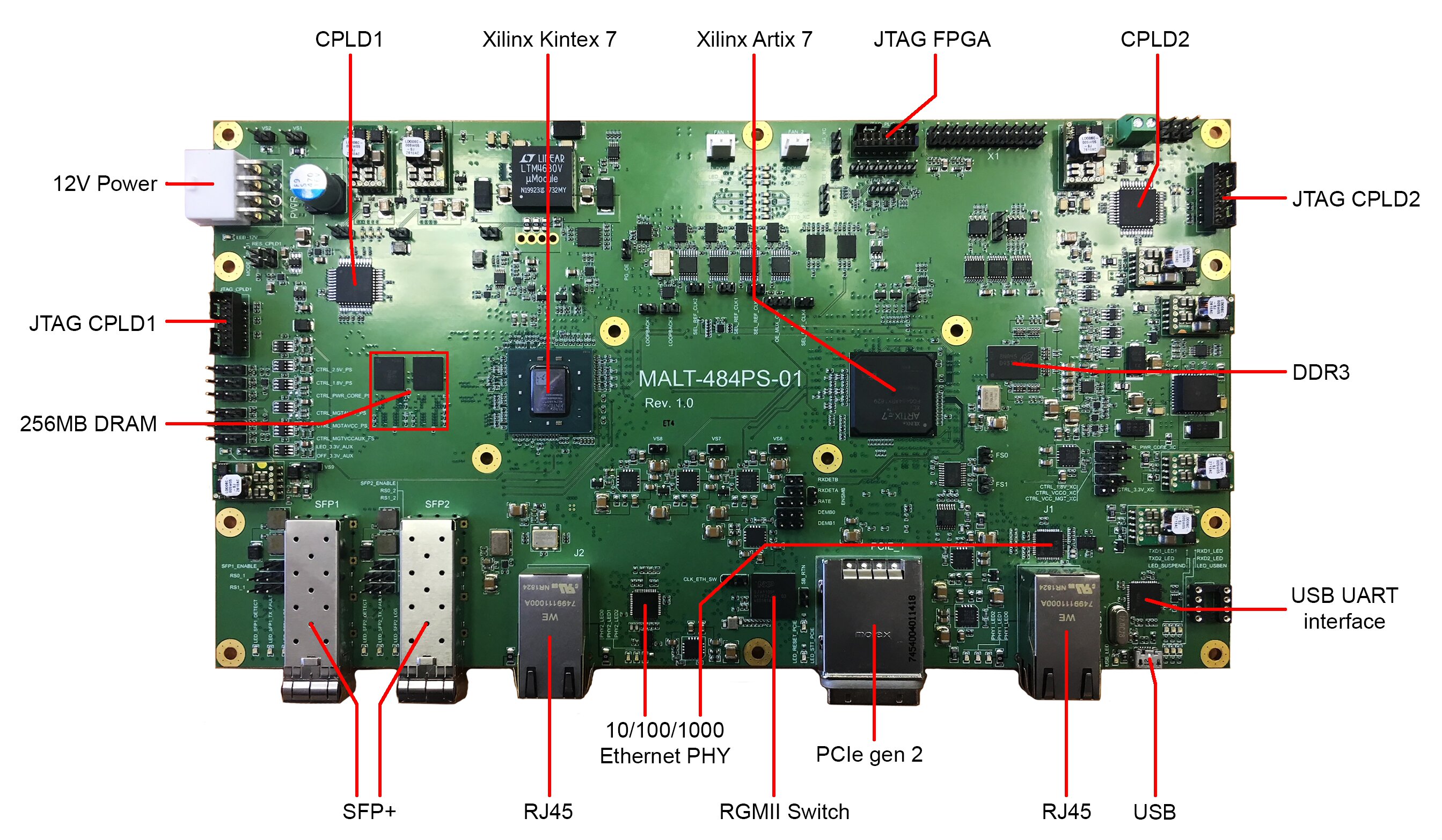

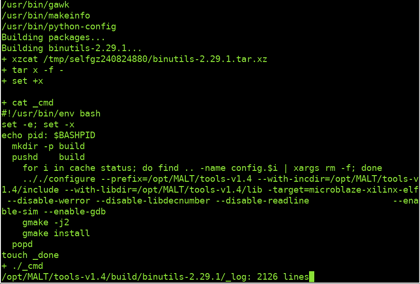

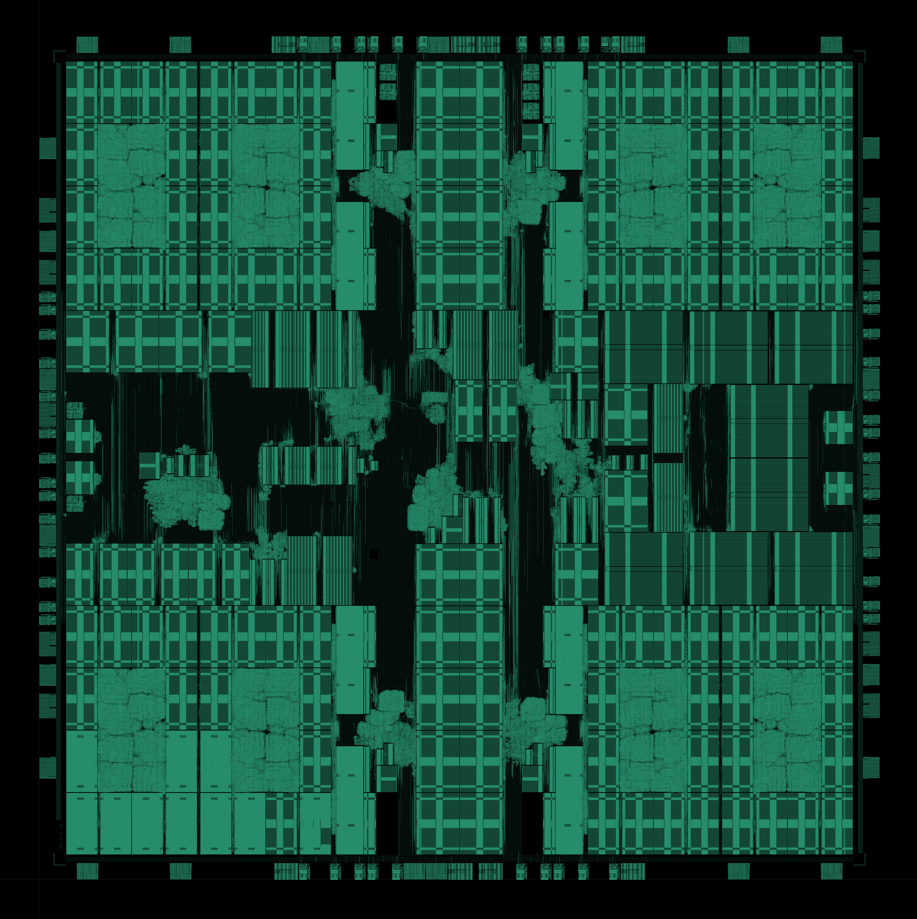

The work related to the design of the MALT-Cv3 processor (Enceladus) was completed in the second quarter of this year. The project was sent to the TSMC factory for the production run of the chip using the TSMC 16 nm technology.