Synthesis of IP block 28 nm has been completed

- Details

- Published: Wednesday, 15 April 2020 10:00

|

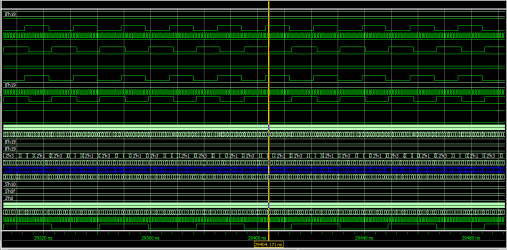

The development of FDPLL is one of the current projects of our company. At this stage of the work, we have successfully completed the synthesis of FDPLL in 28 nm TSMC. The necessary topological representations have been developed and the IP block tests have been completed. The jitter measured in the simulation does not exceed 2% in the output frequency range. Next, we plan to repeat the development in 16 nm TSMC. The required PDK was obtained by our team in early 2020.

Technical specifications

| Parameter | Value |

| Reference frequency, MHz | 0.8-1000 |

| Output frequency, MHz | 200-2000 |

| Auxiliary frequency, MHz | 3.125-1000 |

| Period jitter (max), % | 2 |

| Power, mW | 5 |