- Details

-

Published: Tuesday, 21 March 2017 17:11

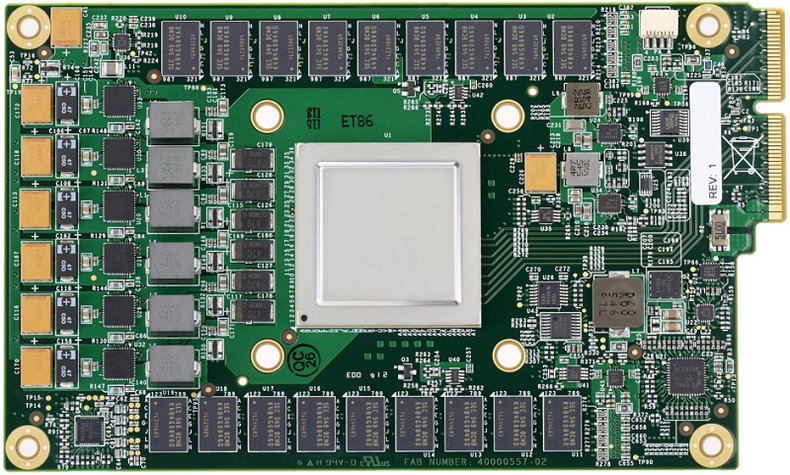

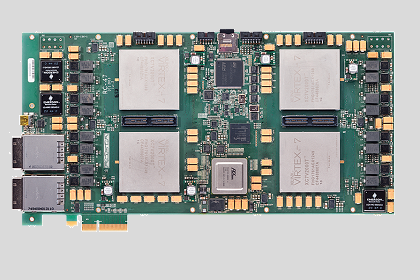

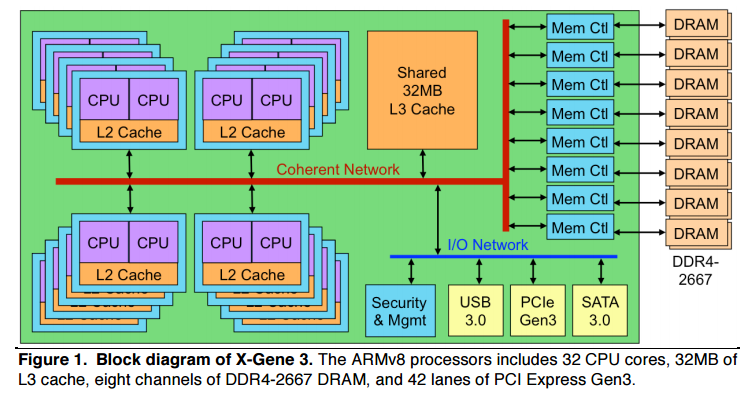

Applied Micro announced it is sampling X-Gene 3, its third-generation ARM SoC for servers. According to a report by The Linley Group, the new platform will provide comparable performance to the latest Intel Xeon processors, but at a significantly lower price point.

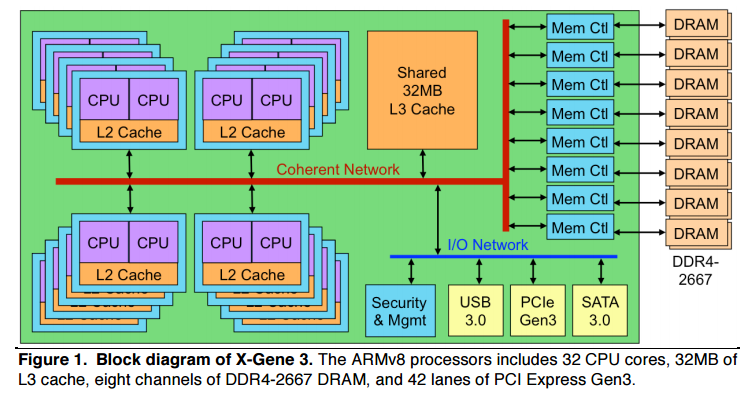

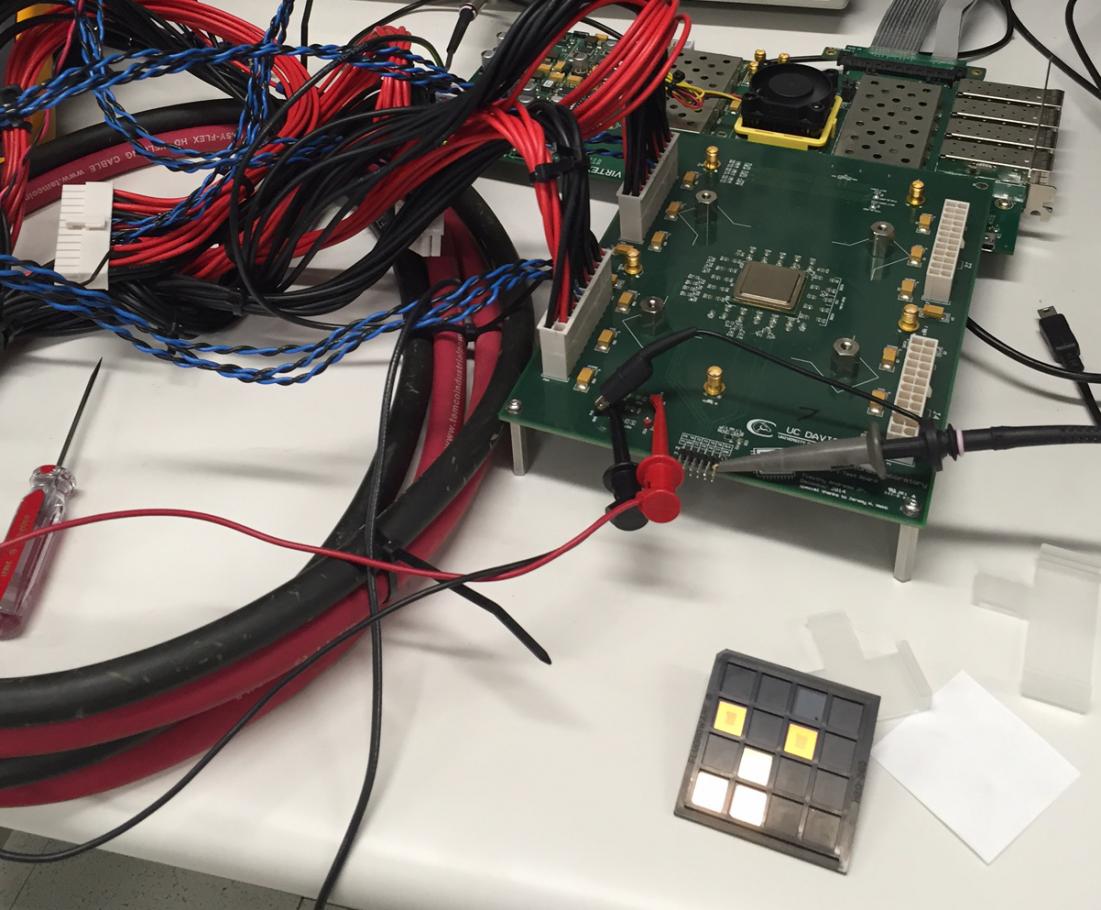

X-Gene 3 respectable performance profile is a result of its relatively high clock speed and memory bandwidth. The CPU runs its 32 cores at a base frequency of 3.0 GHz, and can achieve 3.3 GHz under turbo mode. To feed those cores with data, the chip includes eight memory channels, which can serve DDR4 devices at up to 2667 MHz, yielding 170 GB/sec of aggregate bandwidth. The SoC also includes 42 lanes of PCIe 3.0 links for external connectivity.

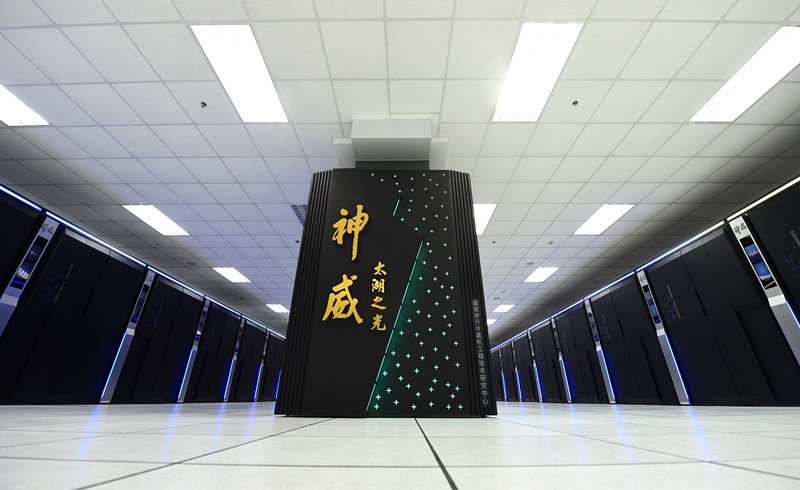

The report states that the X-Gene 3 can handle a “a broad range of cloud workloads, including scale-up and scale-out applications.” It should be particular adept at so-called big data applications like in-memory database processing, thanks to its superior memory bandwidth. Coincidently (or perhaps not), AMD is touting its upcoming “Naples” x86 chip for very similar memory bandwidth capabilities, based on the same 8-channel per socket design.

Read more...