Development of the MALT-Cv3 topology has begun

- Details

- Published: Friday, 15 January 2021 10:00

|

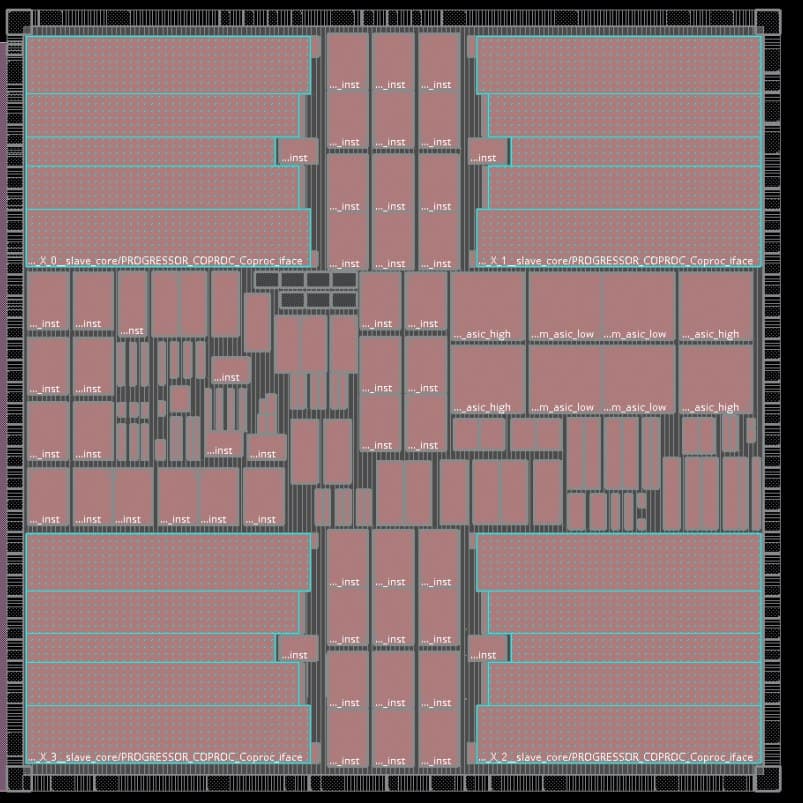

We are pleased to announce that the MALT-Cv3 "Enceladus" processor has been successfully synthesized in the TSMC 16 nm technology base. At the moment, the project is at the stage of topological design. Finalization of the development and tape-out of the MALT-Cv3 "Enceladus" is planned in the second half of 2021. The MALT-Cv3 is designed for streaming network traffic at speeds up to 1 Gbps, including ensuring the security of network connections by programmatically encrypting/decrypting traffic using any user-defined domestic or foreign algorithms. This processor will be our first embedded compact processor focused on streaming on wirespeed.

The processor is based on the MALT-C architecture. Specialized cores designed to speed up the execution of complex mathematical transformations are combined into 4 clusters, each of which contains 16 specialized cores, controlled by a single general-purpose RISC core. The processor has two 1Gb Ethernet controllers for communication with external devices. Both controllers are controlled by a single general-purpose core. Interaction with the processor is carried out through the universal interfaces SPI, UART, GPIO, which are also controlled by a single general-purpose core. 512 KB SRAM memory and up to 64 MB of external HyperRAM/HyperFlash memory are available on the chip. The estimated operating frequency of the processor is 1.2 GHz. The FDPLL of our own development will be used for clocking all subsystems. The predicted power consumption of the chip at full load is 3 W. The first samples of the processor are planned to be released in the first quarter of 2022.

Technical specification

| Parameter | Value |

| General-purpose cores | 7 |

| Specialized cores | 64 |

| Operating frequency, MHz | 1200 |

| Power, W | 3 |

| Package type | BGA |

| Package, mm x mm | 9 x 9 |