The processor for network traffic applications has been sent to the factory

- Details

- Published: Friday, 30 July 2021 10:00

|

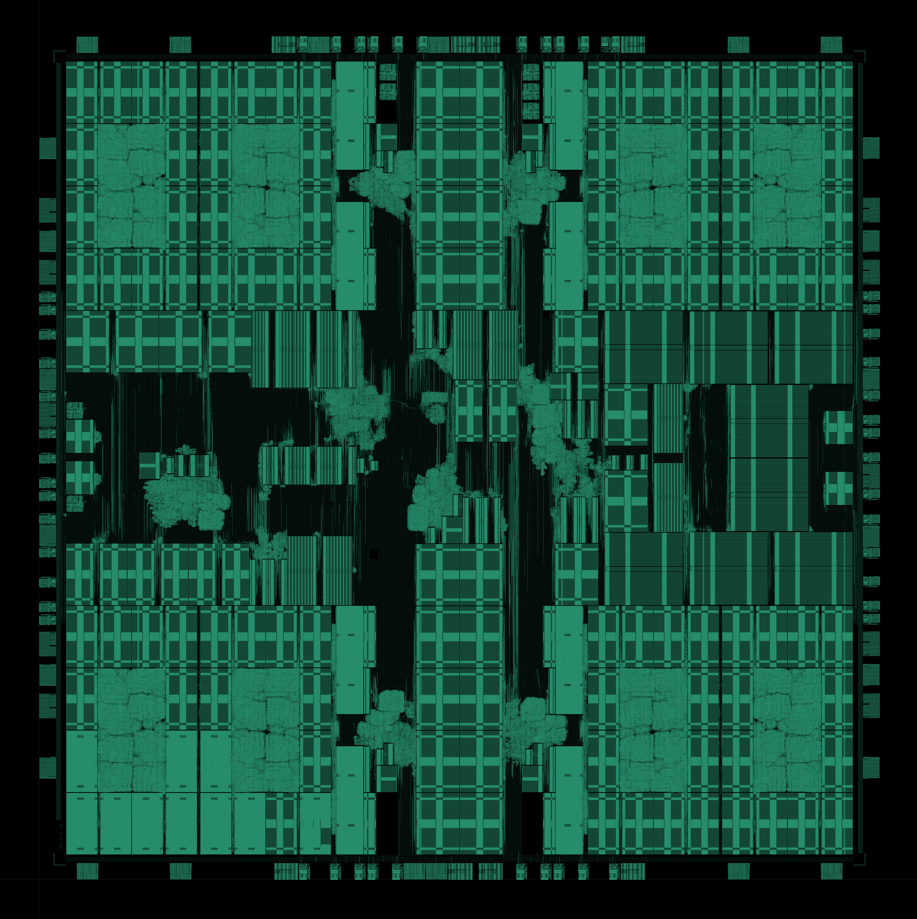

The work related to the design of the MALT-Cv3 processor (Enceladus) was completed in the second quarter of this year. The project was sent to the TSMC factory for the production run of the chip using the TSMC 16 nm technology.

The MALT-Cv3 is designed for processing network traffic at speeds up to 1 Gbps, including network security hardening over application of programmatic encryption/decryption of the traffic using user-defined domestic or foreign cryptoalgorithms.

The MALT-C architecture developed by our team forms the basis for the MALT-Cv3 processor. Specialized cores designed to speed up the execution of complex mathematical transformations are combined into 4 clusters. Each cluster includes 16 specialized cores and is managed by one general-purpose RISC core.

Data exchange with external world is provided via two 1 Gbit Ethernet controllers controlled by single general-purpose computing core. The chip also features SPI, UART and GPIO interfaces and 512 KB of SRAM memory. The estimated operating frequency of the processor is 1.2 GHz. The FDPLL which has been designed by our team as well will be used for clocking all chip subsystems. The predicted power consumption of the chip at full load is approximately 2.8 W.

Technical specification

| Parameter | Value |

| General-purpose cores | 7 |

| Specialized cores | 64 |

| Operating frequency, MHz | 1200 |

| Power, W | 2.8 |

| Package type | BGA |

| Package, mm x mm | 9 x 9 |