16 nm DPLL design completed

- Details

- Published: Saturday, 15 August 2020 10:00

|

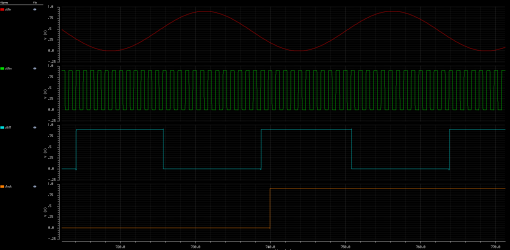

Our company continues to develop FDPLL. At this stage of the work, the FDPLL has been successfully synthesized in 16 nm TSMC. The necessary topological representations have been developed and tests of the generator's IP block have been completed. The jitter measured in the simulation does not exceed 2% in the output frequency range. The 16 nm FDPLL planned to be used as part of a new generation of multi-core MALT processors, including the MALT-Cv3 "Enceladus".

Technical specifications

| Parameter | Value |

| Reference frequency, MHz | 1.2-3000 |

| Output frequency, MHz | 300-3000 |

| Auxiliary frequency, MHz | up to 1500 |

| Period jitter (max), % | 2 |

| Power, mW | 5 |