Завершено проектирование DPLL на 16 нм

- Информация о материале

- Опубликовано: 15.08.2020, 10:00

|

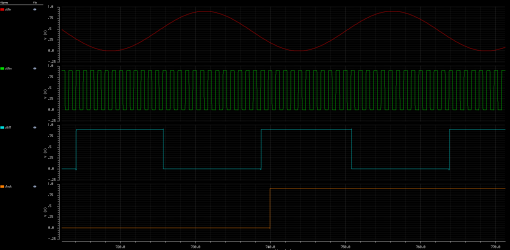

В декабре 2019 наш проект по разработке IP-блока генератора с автоподстройкой частоты получил поддержку от Фонда содействия инновациям. В рамках второго этапа работ успешно проведен синтез FDPLL в технологическом базисе 16 нм TSMC, разработаны необходимые топологические представления, проведены тесты IP-блока генератора. Измеренный в симуляции джиттер не превышает 2% во всем диапазоне выходных частот. IP-блок FDPLL 16 нм планируется использовать в составе многоядерных процессоров MALT нового поколения, в том числе MALT-Cv3 "Энцелад".

Технические характеристики

| Характеристика | Значение |

| Опорная частота, МГц | 1,2-3000 |

| Выходная частота, МГц | 300-3000 |

| Вспомогательная частота, МГц | до 1500 |

| Рабочая частота, МГц | 1200 |

| Джиттер (макс. значение), % | 2 |

| Мощность, мВт | 5 |