Архитектура

Как это работает?

Около 80% любого из разрабатываемых нами кристаллов, занимают однотипные вычислительные элементы, спроектированные “с нуля” специально под целевой класс задач. Эти элементы определяют производительность и энергетику чипа. Их на кристалле от сотен до тысяч! Все вычислительные элементы программируемы на языке С или его подмножестве. Вычислительные элементы объединены в группы, управляемые компактными универсальными RISC процессорами, объединенными в вычислительный массив, “выглядящий” для программиста как обычный, программируемый на C/C++ многопотоковый процессор. Классические проблемы многопоточного программирования (механизмы разрешения конфликтов одновременного доступа к общим данным, в том числе атомарные операции) мы решили аппаратно на уровне контроллера памяти.

Краткий взгляд на архитектуру MALT

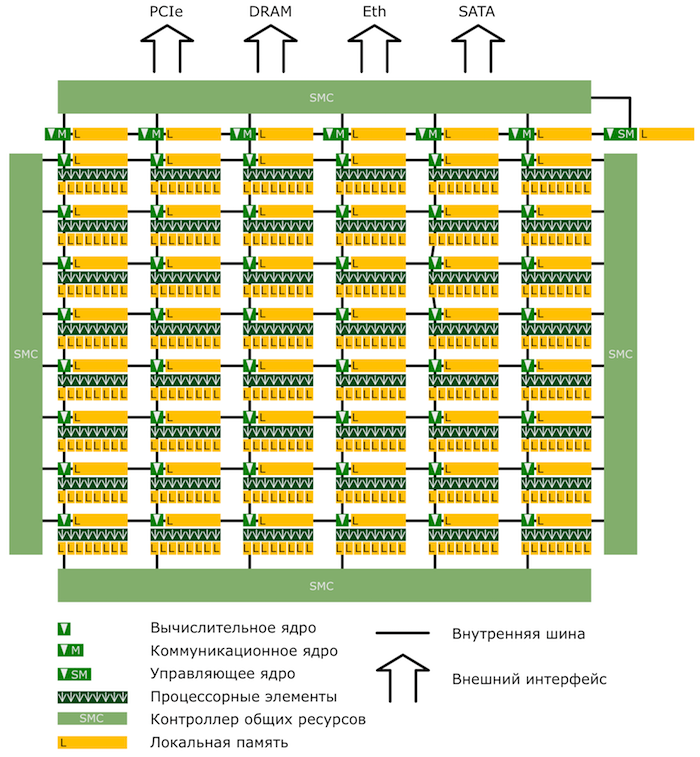

Основу архитектуры MALT составляют десятки или сотни, в зависимости от модели, компактных асинхронных универсальных вычислительных ядер, объединенных одной или несколькими оригинальными worm-hole сетями с топологией типа fat-tree. Коммуникация между сетями - программно-аппаратная. Иерархия универсальных ядер включает три уровня: supermaster - управляющее ядро, master - коммуникационные ядра, slave - доступные для задач пользователя вычислительные ядра. Slave ядра, в зависимости от модели, могут содержать векторные ускорители, выполняющие специализированные задачи целевого класса, каждый ускоритель содержит от 8-ми до 128-ми однотипных процессорных элементов с общей памятью команд. Все вычислительные ядра и ускорители имеют собственную локальную память данных. Все универсальные ядра непосредственно адресуют общую внешнюю динамическую память DRAM и другие общие ресурсы (PCIe, Ethernet, SATA). Арбитраж доступа к внешним ресурсам обеспечивается smart memory controller’ом (SMC) - аппаратным контроллером «умной памяти» с дополнительным признаком готовности данных. Количество SMC-контроллеров, перечень и конфигурация общих внешних ресурсов зависит от семейства MALT и определяется требованиями целевых задач.