IP-блоки

Дизайн-центр MALT разрабатывает цифровые и аналоговые IP-блоки на заказ. Портфолио компании включает в себя как Soft IP-блоки, так и Hard IP-блоки для современных СБИС. IP-блоки создаются под технологический процесс конкретной фабрики. При применении IP-блоков сторонних производителей, нам иногда приходится разрабатывать блоки сопряжения для интеграции в СБИС.

Портфель доступных IP-блоков представлен ниже.

FDPLL

FDPLL (Fully digital glitch free PLL) – это полностью цифровой генератор частоты с автоматической подстройкой без импульсных помех. FDPLL предназначен для создания выходных тактовых импульсов, поэтому идеально подходит в качестве тактового генератора цифровых блоков, но не предназначен для тактирования аналоговых блоков, таких как АЦП/ЦАП или SERDES. FDPLL имеет полностью цифровой дизайн, что позволяет быстро адаптировать его для различных опций технологических норм 28, 16, 7 нм.

ТЕХНИЧЕСКИЕ ХАРАКТЕРИСТИКИ FDPLL 28 нм

| Параметр | Единица измерения | Мин. | Тип. | Макс. | Комментарий |

|---|---|---|---|---|---|

| Опорная частота | МГц | 0.8 | 1000 | ||

| Выходная частота | МГц | 200 | 2000 | ||

| Вспомогательная частота | МГц | 3.125 | 1000 | ||

| Джиттер (по периоду) | % | 2 | CLKO=1000 МГц | ||

| Скважность | % | 45 | 50 | 55 | |

| Мощность | мВт | 5 | CLKO=1000 МГц | ||

| Рабочее напряжение | В | 0.8 | 0.9 | 1.0 | Только цифровое |

| Площадь | мм кв. | 0.012 | |||

| Рабочая температура | C | 0 | 70 | 85 |

ТЕХНИЧЕСКИЕ ХАРАКТЕРИСТИКИ FDPLL 16 нм

| Параметр | Единица измерения | Мин. | Тип. | Макс. | Комментарий |

|---|---|---|---|---|---|

| Опорная частота | МГц | 1.2 | 3000 | ||

| Выходная частота | МГц | 300 | 3000 | ||

| Вспомогательная частота | МГц | 1500 | |||

| Джиттер (по периоду) | % | <2 | CLKO=1000 МГц | ||

| Скважность | % | 45 | 50 | 55 | |

| Мощность | мВт | 5 | CLKO=1000 МГц | ||

| Рабочее напряжение | В | 0.72 | 0.8 | 0.99 | Только цифровое |

| Площадь | мм кв. | 0.0036 | |||

| Рабочая температура | C | -40 | 85 | 125 |

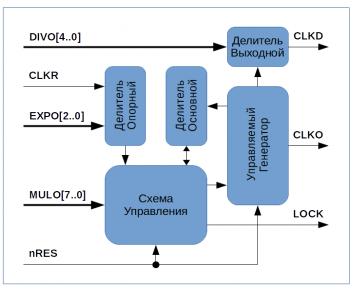

Описание работы

В нормальном состоянии (режим захвата) на выходе генератора CLKO присутствует периодический сигнал с частотой, равной частоте опорного сигнала CLKR, умноженного на величину MULO:EXPO.

MULO:EXPO представляет собой денормализованное число с плавающей точкой, где MULO - 8-битная мантисса, EXPO - 3-битная экспонента. Вместе они дают коэффициент умножения, который рассчитывается следующим образом: код экспоненты EXPO[2..0] переводится в целое число от 0 до 7, которое определяет положение двоичной точки внутри мантиссы MULO[7..0]. Численное значение этого кода представляет собой номер разряда MULO, после которого стоит двоичная точка, разделяющая MULO на целую и дробную части (размер дробной части). То есть для EXPO=0 дробная часть отсутствует, а вся целая часть находится в MULO[7..0]. Для EXPO=7 целая часть находится в MULO[7], дробная в MULO[6..0].

Ограничение: целая и дробная части не могут быть равны нулю одновременно!

MULO[7..0] не может быть полностью нулевым. Остальной выбор коэффициента умножения произволен в диапазоне 0.0000001 до 11111111.0. Однако для достижения оптимальных харектеристик работы DPLL число в MULO не должно быть существенно денормализованным или иметь много нулей в старших разрядах.

В дополнение к основному выходу генератора в модуле имеется вспомогательный выход CLKD, частота которого получается делением основной частоты на коэффициент 2*DIVO[4..0]. Например, значению DIVO = 1 соответствует коэффициент деления D = 2*1, для DIVO = 31, D = 2*31, для DIVO = 0 , D = 2*32.

Таблица. Список выводов

| Сигнал | Направление Гбит/c |

Комментарий Гбит/c |

|---|---|---|

| nRES | вход | Асинхронный сброс (активный низкий уровень) |

| CLKR | вход | Опорная частота |

| MULO[7..0] | вход | Мантисса коэффициента умножения (не может быть полностью нулевым значением) |

| EXPO[2..0] | вход | Экспонента коэффициента умножения (0 - 7) |

| DIVO[4..0] | вход | Коэффициент пост-делителя |

| CLKO | выход | Выходная частота |

| CLKD | выход | Вспомогательная частота после делителя |

| LOCK | выход | Индикация захвата |

| FDPLL 28nm Datasheet |

| Перечень значений коэффициентов умножения для СФ-блока цифрового генератора частоты FDPLL 28nm |

| FDPLL 16nm Datasheet |

Страницы FDPLL 28 nm, 16 nm на сайте design-reuse.com.

Вас интересуют такие IP-блоки как:

- IP-блоки современных криптоускорителей по стандартам DES, AES, SHA и других.

- IP-блоки источников опорного напряжения и термодатчиков (LDO, t).

- IP-блоки высокоскоростных каналов передачи (LVDS, SSTL).

- IP-блоки сериализации данных и восстановления клока (PMA).

- IP-блоки скремблирования и кодирования данных (PCS 8/10, 64/66).

- IP-блоки высокоскоростных последовательных интерфейсов (SERDES).

- IP-блоки логического уровня Ethernet 10/100/1G/10G (Ethernet MAC).

- IP-блоки физического уровня Ethernet 10/100/1G (Ethernet PHY).

- IP-блоки логического уровня DDR 1/2/3 (DDR logic).

- IP-блоки контроллеров памяти RLDRAM (logic).

- IP-блоки контроллеров быстрой статической памяти (QDR SRAM logic).

- IP-блоки периферии (I2C, I2S, SPI, UART и т.д.).

- IP-блоки ЦАП/АЦП, в т.ч. сверхвысокоскоростные.

- IP-блоки для анализа и обработки заголовков сетевых пакетов.

Обращайтесь. Все, указанное выше мы IP-блоки разрабатываем на заказ, часть IP уже готова для применения в ваших проектах. Мы осуществляем послепродажную поддержку в вопросах оптимизации, интерфейсов и совместимости, интеграции IP-блоков в СБИС. Мы предоставляем бесплатные обновления ПО для программируемых IP-блоков нашей разработки.

Мы гарантируем информационную безопасность и правовую чистоту предоставляемых IP-блоков.

Свяжитесь с нами, чтобы узнать больше о возможностях MALT!