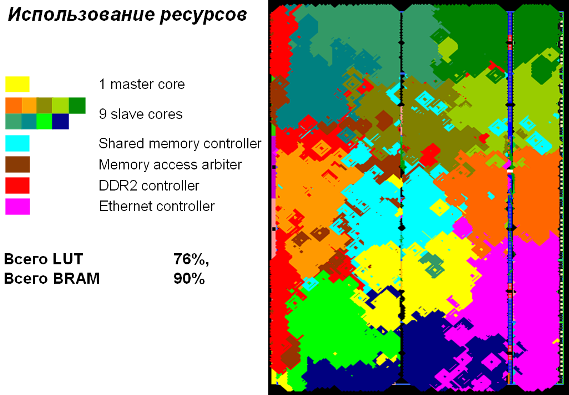

10-core Xilinx Virtex5 processor with tagged shared-memory controller on FPGA has been built

- Details

- Published: Monday, 17 September 2012 23:05

|

|

Finally! We’ve built and tested our first 10-core processor on FPGA.

Technical specification:

- Core frequency - 50 MHz;

- Performance per core (measured using Dhrystone) - 53 DMIPS;

- Local data memory - 8 kB;

- Local instruction cache - 8 kB per core;

- Internal bus width - 128 bit;

- Internal bus frequency - 50 MHz.

For processor design we used the board ML505 Evaluation Platform with Xilinx Virtex-5 XC5VLX50T. It has 256 Mb DDR2 shared external memory and 100 Mbit Ethernet interface. The project utilizes 76% of available LUTs and 90% of BRAM.