Собран 210-ядерный процессор на ПЛИС Xilinx Virtex7

- Информация о материале

- Опубликовано: 28.12.2014, 20:56

|

|

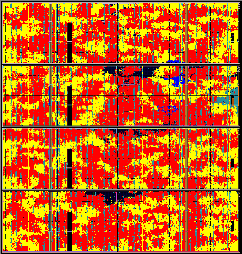

Схема 210-ядерного процессора. Желтым обозначены элементы процессорных ядер, красным - коммуникационные шины, синим - контроллер памяти. Изображение: maltsystem.com |

Недавно мы завершили сборку и отладку нового монстра - прототипа 210-ядерного процессора в ПЛИС Virtex7 2000T. Это самый большой кристалл в седьмом поколении ПЛИС от Xilinx. А наша MALT система - самый большой из известных на сегодня массивов независимых 32-битных RISC ядер, прототипируемых на одном ПЛИС. Настоящий прототип будет использоваться для отладки на реальных задачах контроллера общих ресурсов, в первую очередь "умного" контроллера памяти при сотнях обращений с разных ядер. Такая система также позволит изучить поведение внутрикристальной шины на пиковых нагрузках при различных конфигурациях (количествах цепочек ядре и их длинны).

Технические характеристики текущей версии процессора:

- Частота тактирования ядер - 75 MГц.

- Объем локальной памяти данных - 4 кБайт на ядро.

- Локального кеш команд - 4 кБайт на ядро.

- Разрядность внутренней шины – 128 бит.

- Частота тактирования внутренней шины – 125 МГц.

В качестве внешней памяти может использоваться до 1 Гбит RLDRAMIII. Количество доступной оперативной памяти может быть увеличено за счёт использования памяти хост-компьютера при подключении через PCIe. Максимальный объём памяти в такой конфигурации – 256 ГБайт.

Текущая версия процессора реализована на аппаратной платформе Rosta-RC47, построенной на базе ПЛИС Xilinx Virtex-7 2000T. Проект занимает 59% LUT и 95% BRAM.