Прототип специализированного сетевого процессора готов!

- Информация о материале

- Опубликовано: 01.10.2021, 10:00

|

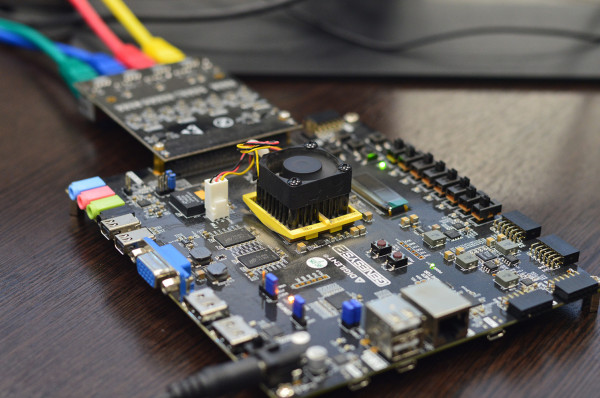

Наш первый прототип специализированного сетевого процессора, наконец, готов! Это масштабный (1:10 по скорости линейных портов и 4:48 по количеству линейных портов) прототип программируемого специализированного сетевого процессора для комплексной обработки трафика в сетях современных центров обработки данных. Прототип собран на ПЛИС Xilinx Kintex7, поддерживает скорость передачи данных 1 Гбит/с на порт на четырех линейных портах. Основная задача настоящего прототипа - продемонстрировать возможность создания в кремнии по технологическим нормам 28/16/12 нм специализированного сетевого процессора с производительностью терабитного уровня и уточнить его характеристики (размер кристалла, энергопотребление, цена при массовом производстве). Разработанный прототип соответсвует стандарту OpenFlow 1.3, за исключением недетерминированных по времени исполнения функций, наподобие разбора инкапсуляций в стандарте заголовка IPv6. Уже проведены первые показы прототипа потенциальным потребителям.

|

Важная задача прототипа - предоставить программистам возможность начать разработку программного стека уже сейчас, не дожидаясь прототипов в кремнии или полноразмерных прототипов на ПЛИС. На разработанном прототипе уже продемонстрирована работа в режиме learning switch с использованием только компонентов с открытым исходным кодом - OpenFlow-оркестратора Ryu и программного коммутатора ivs в качестве middle layer для трансляции правил OpenFlow в загружаемый микрокод сетевого процессора. Также показана работа обработки трафика на полной скорости порта на примере передачи файла между двумя компьютерами с использованием протокола HTTP и алгоритма CUBIC для TCP, использующегося по умолчанию в современных Linux-системах. Установившаяся скорость скачивания составила 105 Мбайт/с при работе встроенного трафик-полисера с политикой tail-drop, что соответствует максимальному теоретическому значению. На прототипе продемонстрированы произвольные модификации обрабатываемого трафика на примере MPLS-меток и тегов VLAN (добавить метку для метки X, изменить метку для метки Y, тегировать VLAN’ом V метку Z, удалить метку).

|

Для нас это лишь первый шаг. Мы планируем создать в кремнии семейство коммутаторов с программным управлением c производительностью коммутации в сечении до 1 Тбит/с на wire-speed и 1.3 млрд пакетов/с на устройство с возможностью выполнения произвольных, в том числе не существующих на сегодняшний день, алгоритмов классификации и преобразования сетевого трафика без потерь в производительности. Разработка ведется под технологический процесс TSMC 28/16/12 нм. В наших устройствах мы реализуем нативную поддержку протокола P4 с возможностью управления набором правил обработки трафика через RPC доступную, в том числе, на настоящем прототипе и, конечно, поддержку стандартных протоколов маршрутизации и коммутации сетевого трафика.

|

На картинке выше приведен предварительный рендер программируемого коммутатора в форм-факторе 1U на базе описанного выше сетевого процессора, на лицевую панель вынесены 48 портов 10GE/SFP+ и 4 порта 100GE/QSFP28. Следите за новостями развития нового отечественного семейства сетевых процессоров на нашем сайте!