Архитектура MALT представлена на конференции в Высшей Школе Экономики

- Информация о материале

- Опубликовано: 08.06.2018, 12:28

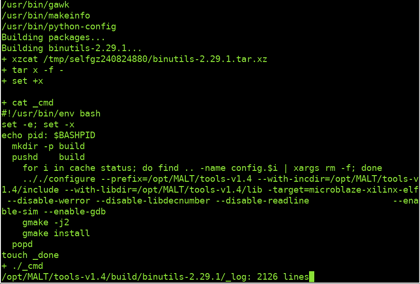

Архитектура MALT была представлена на VI Международной научно-практической конференции «Управление информационной безопасностью в современном обществе», прошедшей в "Высшей Школе Экономике" 5-7 июня.